基于CMOS多功能数字芯片的ESD保护电路设计

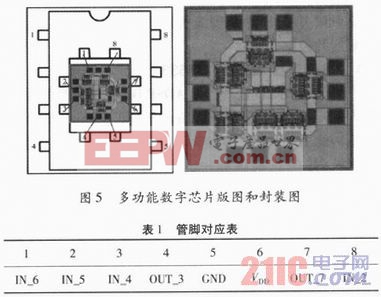

napback状态,具有较强的电流泄放能力和较低的维持电压。 图5所示为一款多功能数字芯片的版图照片和封装示意图,表1为管脚对应图。在多功能数字芯片的设计中,在输入端使用了设计的ESD保护电路,另外,由于所设计的多功能数字芯片,在输出端设计了尺寸较大的MOS管构成的反相器来提高芯片的驱动能力,这些MOS管的漏区和衬底形成的pn结就相当于一个大面积的二极管,可以起到ESD保护作用。因此,一般可不用增加ESD保护器件,但由于需要在芯片流片后首先进行在片测试,所以在芯片的输出端加上了与输入端同样的ESD保护电路。

2 ESD保护电路

对深亚微米CMOS集成电路,栅氧化层的击穿电压很小,常规二极管的击穿电压较大,不能起到很好的保护作用。因此可以增加离子注入提高二极管的衬底浓度,形成p+n+和n+p+结构来降低二极管的击穿电压。

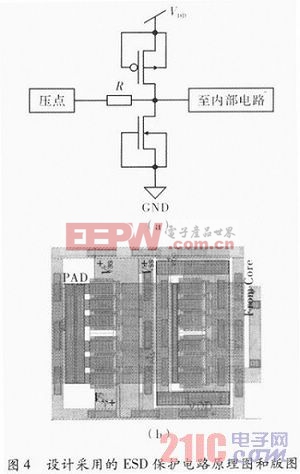

考虑到准备流片的多功能数字芯片要采用CSMC2P2M 0.6μm标准的COMS工艺,在设计中采用了如图4所示的ESD保护电路,用一个栅接地的NMOS管和一个栅接VDD的PMOS管共同构成输入ESD保护电路。另外,由于设计的ESD保护电路的MOS官尺寸大,所以在版图上画成多个插指,同时由于保护电路的MOS管尺寸较大,其漏源区pn结又可以起到二极管保护作用。图4所示为设计采用的ESD保护电路的原理图和版图。

3 ESD保护电路在流片后的测试情况

图6所示为流片后的多功能数字芯片的在片测试波形,由测试波形可以看出,ESD保护电路对多功能数字芯片起到保护作用。

系统介绍了ESD保护电路;分析了不同的传统ESD保护电路的设计原理和优缺点。在此基础上,基于CSMC 2P2M 0.6μm标准的COMS工艺,进行ESD保护电路的版图设计和验证,并在一款多功能数字芯片上应用,该芯片参与了MPW计划进行流片。测试结果显示该ESD保护电路能直接应用到各种集成电路芯片中。

ESD 保护 电路设计 芯片 数字 CMOS 多功能 基于 相关文章:

- 工程师针对手机的先进ESD与EMC的保护解决方案(01-12)

- 手机设计中的抗电磁干扰EMI和ESD防护技术(12-06)

- 利用HFTA-16.0建立双极型集成电路的ESD保护(11-28)

- 合理的PCB布线准则 ESD防护总结(11-20)

- 使用BUS端口保护阵列实现有源ESD保护(10-05)

- 浅叙ESD保护二极管的效果(05-16)