合理的PCB布线准则 ESD防护总结

在PCB设计中,由于采用了瞬态电压抑止器二极管来抑止因ESD放电产生的直接电荷注入,因此PCB设计中更重要的是克服放电电流产生的电磁干扰,本文主要讲解可以优化ESD防护的PCB设计准则。

电路环路

电流通过感应进入到电路环路,这些环路是封闭的,并具有变化的磁通量。电流的幅度与环的面积成正比。较大的环路包含有较多的磁通量,因而在电路中感应出较强的电流。因此,必须减少环路面积。

图1:最常见的环路电路

最常见的环路如图1所示,由电源和地线所形成。在可能的条件下,可以采用具有电源及接地层的多层PCB设计。多层电路板不仅将电源和接地间的回路面积减到最小,而且也减小了ESD脉冲产生的高频EMI电磁场。

图2:电源线和接地线连接图

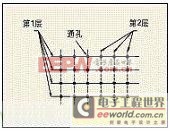

如果不能采用多层电路板,那么用于电源线和接地的线必须连接成如图2所示的网格状。网格连接可以起到电源和接地层的作用,用过孔连接各层的印制线,在每个方向上过孔连接间隔应该在6厘米内。另外,在布线时,将电源和接地印制线尽可能靠近也可以降低环路面积,如图3所示。

图3:将电源和接地印制线尽可能靠近也可以降低环路面积 减少环路面积及感应电流的另一个方法是减小互连器件间的平行通路,见图4。

图 4:减小互连器件间的平行通路

当必须采用长于30厘米的信号连接线时,可以采用保护线,如图5所示。一个更好的办法是在信号线附近放置地层。信号线应该距保护线或接地线层13毫米以内。

图5:当必须采用长于30厘米的信号连接线时,可以采用保护线

如图6所示,将每个敏感元件的长信号线(>30厘米)或电源线与其接地线进行交叉布置。交叉的连线必须从上到下或从左到右的规则间隔布置。

图6:将每个敏感元件的长信号线(>30厘米)或电源线与其接地线进行交叉布置 电路连线长度

长的信号线也可成为接收ESD脉冲能量的天线,尽量使用较短信号线可以降低信号线作为接收ESD电磁场天线的效率。

尽量将互连的器件放在相邻位置,以减少互连的印制线长度。

地电荷注入

ESD对地线层的直接放电可能损坏敏感电路。在使用TVS二极管的同时还要使用一个或多个高频旁路电容器,这些电容器放置在易损元件的电源和地之间。旁路电容减少了电荷注入,保持了电源与接地端口的电压差。

TVS使感应电流分流,保持TVS钳位电压的电位差。TVS及电容器应放在距被保护的IC尽可能近的位置(见图7),要确保TVS到地通路以及电容器管脚长度为最短,以减少寄生电感效应。

连接器必须安装到PCB上的铜铂层。理想情况下,铜铂层必须与PCB的接地层隔离,通过短线与焊盘连接。

PCB设计的其它准则

1. 避免在PCB边缘安排重要的信号线,如时钟和复位信号等;

2. 将PCB上未使用的部分设置为接地面;

3. 机壳地线与信号线间隔至少为4毫米;

4. 保持机壳地线的长宽比小于5:1,以减少电感效应;

5. 用TVS二极管来保护所有的外部连接;

保护电路中的寄生电感

TVS二极管通路中的寄生电感在发生ESD事件时会产生严重的电压过冲。尽管使用了TVS二极管,由于在电感负载两端的感应电压VL=L×di/dt,过高的过冲电压仍然可能超过被保护IC的损坏电压阈值。

保护电路承受的总电压是TVS二极管钳位电压与寄生电感产生的电压之和,VT=VC+VL。一个ESD瞬态感应电流在小于1ns的时间内就能达到峰值(依据IEC 61000-4-2标准),假定引线电感为每英寸20nH,线长为四分之一英寸,过冲电压将是50V/10A的脉冲。经验设计准则是将分流通路设计得尽可能短,以此减少寄生电感效应。 所有的电感性通路必须考虑采用接地回路,TVS与被保护信号线之间的通路,以及连接器到TVS器件的通路。被保护的信号线应该直接连接到接地面,若无接地面,则接地回路的连线应尽可能短。TVS二极管的接地和被保护电路的接地点之间的距离应尽可能短,以减少接地平面的寄生电感。

最后,TVS器件应该尽可能靠近连接器以减少进入附近线路的瞬态耦合。虽然没有到达连接器的直接通路,但这种二次辐射效应也会导致电路板其它部分的工作紊乱。

- 适合高效能模拟应用的线性电压稳压器(07-19)

- 构建一个低成本的9V电池电压监控器(07-28)

- 主动“ORing”方案降低了功率损耗和设备尺寸(06-24)

- 开关电源要降低纹波主要要在三个方面下功夫(06-24)

- TI以独特的芯片结构和散热封装叩关功率MOSFET市场(01-26)

- DC/DC电源管理应用中的功率MOSFET的热分析方法(12-10)