探讨电磁干扰和射频干扰及其抑制措施

源隔离、数字/模拟的高频部分与低频部分相互隔离。采用多层板可减小EMI发射,且对RF场的抗扰度要比双面板增加10倍或更多。比较好的多层板排列是将信号线嵌入在电源层和地线层之间,这种设计的优点是低阻抗、低辐射、低串扰,可减小50MHz以上的辐射和串扰,但板内容量小,退耦困难,嵌入信号线的测试与检修困难。

(3)PCB中走线的特性阻抗。为了防止反射,要求PCB上走线的特性阻抗应满足单向传输延迟时间等于或大于信号上升/下降时间的一半。为此,一般应采用2英寸/ns准则。表3给出了常用数字逻辑基于2英寸/ns准则的走线长度。2英寸/ns准则也适用于模拟电路的走线设计。

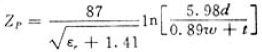

对于利用绝缘材料将信号层与电源/电线层隔离的PCB板的特性阻抗可用下式计算:

式中εr为PCB板材料介电常数;d为各层的厚度(mils);w为线宽(mils);t为线厚(mils)。

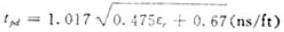

信号层走线的单向传输时间由下式确定:

例如:一个标准4层PCB板,一般利用0.021〃FR-4(εr=4.7)型绝缘材料隔离,采用8mil宽、1.4 mil厚的铜层走线,其特性阻抗为88Ω,单向传输时间为1.7 ns/ft。

总之,在PCB设计时,必须按实际情况和可能大些,将信号线间隙用地线填充。电源和地线采用平行走线,有利于减小电感。

7、屏蔽技术

屏蔽技术可防止外部EMI/RFI对电路或系统的影响,但要正确应用屏蔽技术,就必须清楚干扰源、环境、干扰源与被干扰对象之间的距离等问题。如果电路或系统靠近干扰源,电磁场特性取决于干扰源;如果电路远离干扰源,电磁场特性取决于传输介质。当电路与干扰源的距离小于λ/2π(λ为干扰信号波长)时,就认为电路靠近干扰源,否则,认为远离干扰源。

EMI/RFI对电路的影响与其特性阻抗有关,电磁场的特性阻抗(波阻抗)取决于电场和磁场之比。对于远电磁场,其电磁比率就是空气的波阻抗(Z=377Ω);对于近电磁场,波阻抗取决于干扰的固有特性及距干扰源的距离,如果干扰是高电流低电压,则磁场占主要地位,波阻抗小于377Ω,如果干扰是低电流高电压,则电场起主要作用,波阻抗大于377Ω。通常采用封闭导体对电路进行屏蔽,封闭导体对电路屏蔽的有效性取决于屏蔽材料表面对入射波的反射损耗和屏蔽体对内部发射波的吸收损耗。对于电场,反射损耗取决于干扰频率和屏蔽材料,即

适当的封闭屏蔽体对防止外部干扰和限制内部干扰是很有效的,然而,在实际工程中,由于内部电路中的调节旋纽、开关、连接器及通风大呢感原因,经常需要在屏蔽体上开设槽孔,这将削弱屏蔽性能,导致干扰进入系统内部。这种情况下的屏蔽效率为:屏蔽效率

式中λ为干扰信号的波长;L为槽孔的最大长度。

当屏蔽体哂纳感所开槽孔的最大长度等于干扰频率波长的一半时,辐射最大,相当于没有屏蔽效果。为此,在屏蔽体上开设槽孔时,其最大长度要小于干扰信号波长的1/20,同时应在多个面开设而不是在一个面开设槽孔。

8、结论

在日益复杂的电磁环境下,如何减小相互间的电磁干扰,使各种设备和系统能正常运转,是一个亟待解决的问题。在采用不同的方法对EMI/RFI精心抑制时,应分析其综合效应,并对所采用的干扰抑制手段的作用进行恰当的预估,才能获得较理想的效果。

作者:李贵山、杨建平、黄晓峰

9、参考文献

1)、H W Ott.Noise Reduction Techniques in Electronic Systems.Second Editiong.New York,John Wiley&Sons,Inc.,1988

2)、A Rich.Understanding Interference-Type Noise.Ana-log Dialogue,1982,16(3):16~19

3)、A Rich.Shielding and Guarding.Analog Dialogue,1983,17(1):8~13

- 电磁干扰与电磁兼容浅谈(一)(连载)(01-10)

- 电磁干扰滤波器综述(12-07)

- 开关电源电磁干扰源分析(01-19)

- 电磁干扰与电磁兼容浅谈(二)(连载)(01-10)

- 电子设计应该掌握的电磁干扰与电磁兼容基础知识(05-22)

- 电磁干扰(EMC)的屏蔽方法(04-02)