提升单相同步降压转换器效率的设计技巧

6636是因为它的栅极电荷(QG)低,开关损耗最校对于输入至输出的降压比很高的特定场合,高压侧MOSFET保持导通的

时间不长,大部分损耗是开关损耗。

输入和输出电容的选择要满足总体瞬态目标,并使输入和输出纹波电流最小。对于高纹波电流,电感值小可能导致非常大的输出电压纹波。同样,如果瞬态负载阶跃很大,当电感电流斜坡上升或下降到新的稳态输出电流值时,需要相对大的电容值来使输出电压偏移最小。

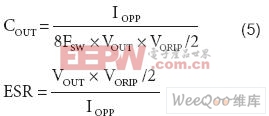

作为起点,把输出电压纹波的一半分配给电容器ESR,另一半分配给电容,如下式所示:

假设1V输出电压的目标纹波为3mV,根据式5计算出COUT为3000μF。为提供一些设计余量,选择输出电容为4400μF。输入电容主要由降压转换器输入端的纹波电流决定,该纹波用下式确定:

RMS纹波电流的计算如下:

输入电容额定值应该为以上计算出的纹波电流的1.4倍,以确保有50%的降额。建议使用额定电压等于最高预期输入电压的1.1倍、ESR低的X7R或X5R电介质陶器。可以采用陶瓷和低ESR有机或聚合物电解电容的组合来降低成本和体积。通过把以上计算出的总纹波电流应用于所有的输入电容上,可以确定每个元件的纹波电流。采用电流分流公式计算每个电容的纹波电流时,应该考虑每个电容在开关频率下的阻抗。

通过采用上述方法,所选择的元件都针对给定工作条件进行了优化,同时也针对成本进行了优化。设计工程师总是倾向花更多的钱购买更好的低损耗元件来进一步提高效率,然而,实用的商用方案可以在增加的成本仅占总电路成本一小部分的情况下提高效率。

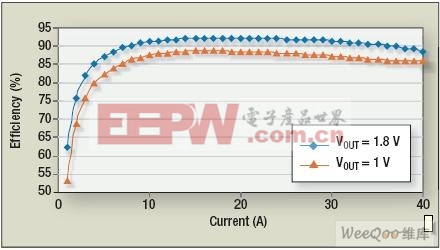

图3给出了该降压转换器的测量效率。对于20A额定电流时的1.8V输出,转换效率高达92%以上,即使在最大电流(40A)时的曲线也非常平坦。这种高效率特性是通过多种方法来实现的。首先是采用了Zilker Labs公司的栅极驱动控制算法,并针对高压侧和低压侧MOSFET分别将死区时间动态调节到4ns和8ns。当固定死区时间时,设计工程师不得不增大这些值,以将任何工艺偏差都考虑进去并避免出现交叉导通。额外的死区时间将导致低压侧MOSFET中体二极管的传导损耗更大。

另一个原因是采用MOSFET并联来减少寄生电感、降低总电阻并提供更好的散热。本例采用了两个高压侧和两个低压侧MOSFET。减少MOSFET数量将增加传导损耗,而增加MOSFET数量则会增加开关损耗。

由于采用了专利引脚跨接技术,ZL2005的大多数配置和设置都无需使用任何外部元件,这就降低了功率损耗,并为改进热性能提供更大的铜面积。驱动器强度和速度允许采用低电阻MOSFET,且不会影响效率。

电流大于20A~30A的应用一般地采用两相方案设计。单相方案的缺点是增加了电流纹波,本例的额定输入纹波比典型的两相方案大50%。

在两相方案中,虽然给定瞬态性能对输出电容的要求较低,但输出纹波也将降低。但是,在此电流下,选择输出电容器主要由电容器的总体电阻(ESR)来决定,需要的元件数量相差不多。两相方案也需要复杂的电流平衡算法,以确保两相电流相同。布局将变得更加重要,这也意味着要使用额外引脚来获取电流共享信息。

采用这个单相设计所达到的动态性能完全满足设计目标。从30A到40A的10A负载阶跃(2.5A/μs)会产生±30mV (为VOUT的3%)的输出电压偏移。表2对最近推出的多个20A到30A方案作了比较。

本设计在降低系统复杂性的同时,还将效率提高了2%至4%。

- 1200V CoolSiCTM MOSFET兼具高性能与高可靠性(06-28)

- 如何借用同步整流架构提高电源转换器效率(12-09)

- 高端准谐振零压开关反激式转换器中的ESBT技术(12-09)

- A→D 转换器的保真度测试(12-09)

- 如何通过配置负载点转换器 (POL) 提供负电压或隔离输出电压(12-09)

- 基于LNK302/LNK304-306离线转换器的非隔离电源及恒流LED驱动器(12-08)