基于反相SEPIC的高效率降压/升压转换器的设计

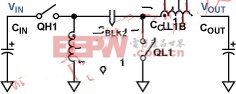

许多市场对高效率同相DC-DC转换器的需求都在不断增长,这些转换器能以降压或升压模式工作,即可以将输入电压降低或提高至所需的稳定电压,并且具有最低的成本和最少的元件数量。反相SEPIC(单端初级电感转换器)也称为Zeta转换器,具有许多支持此功能的特性(图1)。对其工作原理及利用双通道同步开关控制器ADP1877的实施方案进行分析,可以了解其在本应用中的有用特性。

图1. 反相SEPIC拓扑结构

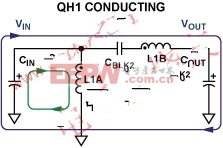

初级开关QH1和次级开关QL1反相工作。在导通时间内,QH1接通,QL1断开。电流沿两条路径流动,如图2所示。第一条路径是从输入端经过初级开关、能量传输电容(CBLK2)、输出电感(L1B)和负载,最终通过地流回输入端。第二条路径是从输入端经过初级开关、地基准电感(L1A)和地流回输入端。

图2. 电流流向图;QH1闭合,QL1断开

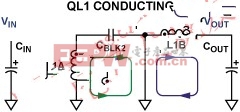

在关断期间,开关位置刚好相反。QL1接通,QH1断开。输入电容(CIN)断开,但电流继续经过电感沿两条路径流动,如图3所示。第一条路径是从输出电感经过负载、地和次级开关流回输出电感。第二条路径是从地基准电感经过能量传输电容、次级开关流回地基准电感。

图3. 能量传输图;QL1闭合,QH1断开

应用电感伏秒平衡原理和电容电荷平衡原理,可以求得方程式1所规定的均衡直流转换比,其中D为转换器的占空比(一个周期的导通时间部分)。

(1)

上式表明:如果占空比大于0.5,输出端将获得较高的调节电压(升压);如果占空比小于0.5,调节电压会较低(降压)。此外还可分析得到其它相关结果:在无损系统中,能量传输电容(CBLK2)上的稳态电压等于VOUT;流经输出电感(L1B)的直流电流值等于IOUT;流经地基准电感(L1A)的直流电流值等于IOUT × VOUT/VIN。该能量传输电容还能提供VIN至VOUT的隔直。当存在输出短路风险时,此特性很有用。

分析还显示,反相SEPIC中的输出电流是连续的,对于给定输出电容阻抗,会产生较低的峰峰值输出电压纹波。这就允许使用较小、较便宜的输出电容;相比之下,在非连续输出电流拓扑结构中,为了达到同样的纹波要求,需要使用较大且昂贵的电容。

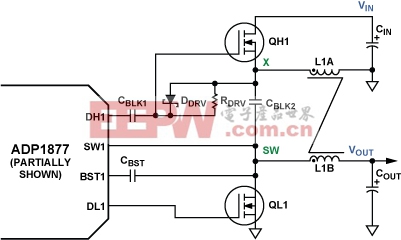

通常,次级开关(QL1)是一个单向功率二极管,它会限制这种拓扑结构的峰值效率。然而,利用ADI公司双通道同步开关控制器ADP1877(见附录)的一个通道,并采用双向MOSFET作为次级开关,可以设计一个“完全同步配置”的反相SEPIC。这样,峰值效率将大大提高,同时可以降低输出电流大于1 A的转换器尺寸和成本。

图4显示完全同步反相SEPIC配置的功率级,它利用ADP1877实现,只需要三个小型、廉价的额外器件(CBLK1、DDRV和RDRV),其功耗可以忽略不计。

图4. 同步反相SEPIC的功率级,利用ADP1877的通道1实现

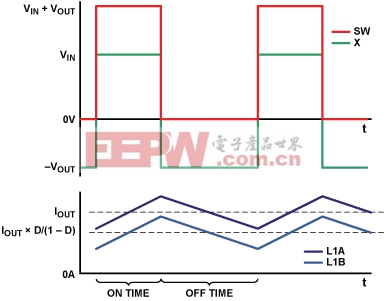

反相SEPIC的理想稳态波形如图5所示。通道1开关节点SW1(见附录图A)在VIN + VOUT (导通时间内)和0 V(关断时间内)之间切换。将电荷泵电容CBST, 连接到SW1,以便在导通时间内将约为VIN + VOUT + 5 V的电压施加于高端内部驱动器的自举上电轨(BST1引脚)和高端驱动器的输出(DH1引脚),从而增强初级浮空N沟道MOSFET开关QH1。箝位二极管DDRV, 确保稳态输出期间CBLK1上的电压约为VOUT + VFWD(DDRV),该电压参考ADP1877的DH1引脚到QH1栅极的电压。在关断时间内,当X节点电压约为–VOUT时,CBLK1上的电压阻止初级开关产生高于其阈值的栅极-源极电压。

图5. 同步反相SEPIC的理想波形(忽略死区)

ADP1877具有脉冲跳跃模式,使能时,可以降低开关速率,只向输出端提供足以保持输出电压稳定的能量,从而提高小负载时的效率,大大降低栅极电荷和开关损耗。在同步反相SEPIC和同步降压拓扑结构中均可以使能此模式。图4所示DC-DC转换电路只需要双通道ADP1877的一个通道,因此另一通道可以用于任一种拓扑结构。

电感耦合和能量传输电容

图4中,功率电感L1A和L1B显示为彼此耦合。在这种拓扑结构中,耦合电感的目的是减少输出电压和电感电流的纹波,并且提高最大可能闭环带宽,下一部分将对此加以说明。

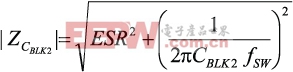

虽然这些电感互相耦合,但并不希望耦合太紧,以至于将一个绕组的大量能量通过铁芯传输至另一个绕组。为了避免这一点,必须求得耦合电感的泄漏电感(LLKG),并选择适当的能量传输电容(CBLK2),使得其复数阻抗的幅值为泄漏电感与单个绕组电阻(DCR)的复串联阻抗的1/10,如方程式2、3、4所示。按照这一关系设计电路,可使耦合铁芯所传输的能量降至最低。泄漏电感可以根据耦合电感数据手册中提供的耦合系数计算。

(2)

(3)

(4)

匝数比最好为1:1,因为对于给定水平的输出电压纹波,此时各绕组只需要分立电感所需电感的一半1。可以使用1:1以外的

- 1200V CoolSiCTM MOSFET兼具高性能与高可靠性(06-28)

- 如何借用同步整流架构提高电源转换器效率(12-09)

- 高端准谐振零压开关反激式转换器中的ESBT技术(12-09)

- A→D 转换器的保真度测试(12-09)

- 如何通过配置负载点转换器 (POL) 提供负电压或隔离输出电压(12-09)

- 基于LNK302/LNK304-306离线转换器的非隔离电源及恒流LED驱动器(12-08)