滞流控制实现LED恒流驱动

摘 要: 设计了一款降压型L ED 恒流驱动芯片的滞环控制电路。 该芯片采用高边电流检测方案,运用滞环电流控制方法对驱动电流进行滞环控制,从而获得恒定的平均驱动电流。 设计采用简单的设计理念实现恒流驱动,不需要复杂的电路分析,能实现精确的电流控制,且自身具有稳定性。 芯片采用0. 5μm 5V/ 18V/ 40V CDMOS 工艺研制,电源电压范围为4.5V~28V ,工作温度-40 ℃~125 ℃,可为L ED 提供恒定的350mA 驱动电流,通过调节外部检测电阻,可调节恒定L ED 驱动电流。 外部提供DIM 信号,通过DIM 的占空比来调节L ED 的亮度。 Hspice 仿真结果显示:L ED 驱动电流为滞环变化的三角波,恒流精度小于6. 2 %。

1 引言

L ED(Light Emitting Diode)作为一种节能环保的绿色照明技术,在通用照明、背光照明、闪光灯、屏幕显示、信号指示及交通工具等方面有广泛的应用。相对于传统照明光源,L ED 优势明显,如高发光效率、高响应速度、耗电量少、体积小、寿命长等。目前,L ED 的驱动方式有恒压和恒流驱动两种,其中,恒流驱动是常用方式。 恒流驱动消除温度和工艺等因素引起正向电压变化所导致的电流变化,保证恒定的L ED 亮度。 在L ED 恒流驱动控制模式中,滞环电流控制模式具有诸多优点: 结构简单、自稳定、不易因噪声而发生不稳定振荡[7 ]等,使用日益广泛。 MAXIM 公司的MAXIM16819 就是L ED 恒流驱动芯片。

文中实现了一种简单的滞流控制模块,通过模块内部自建滞环比较电压, 结合DIM 控制端的PWM 信号控制功率开关管的通断,实现对L ED 的恒流控制。

2 电路设计与原理分析

2. 1 滞环控制原理

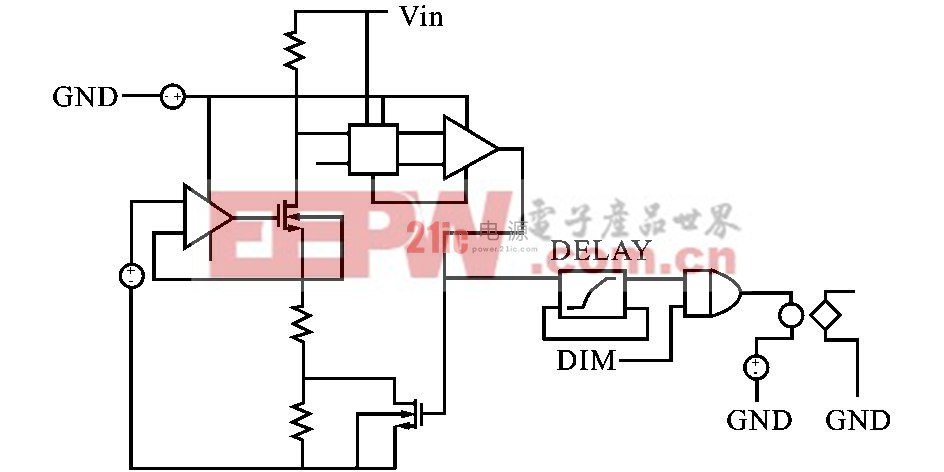

滞流控制模块应用如图1 所示,L ED 驱动电流的变化反应在检测电阻RSENSE两端的压差变化上。 本设计中,检测电阻设为0. 5Ω ,较小的检测电阻有利于降低功耗和保持较高的转换效率。 滞环电流控制模块内部自建两个电压阈值,检测电压Vcs与阈值电压进行比较,比较结果和DIM 调光信号相与来控制功率开关管的通断。

图1 滞流控制模块应用图示

使用PWM 调光, 在减少电流占空周期内给L ED 提供完整电流, 例如要将亮度减半, 只需在50 %的占空周期内提供完整的电流。 通常PWM 调光信号的频率会超过100Hz ,以确保这个脉冲电流不会被人眼所察觉。

滞流控制模块内部电路如图2 所示,当DIM 信号为高电平期间,当Vcs 大于上电压阈值时,控制电路输出低电平,关闭功率开关管。 由LED、电感L 、续流二极管D 和RSENSE组成的回路使得电感继续为L ED 提供电流,电感电流逐渐减小,使得检测电压Vcs 随之减小;当Vcs 小于下阈值电压时,控制电路输出高电平,导通功率开关管,此时D 截止,形成从电源经RSENSE、L ED、L 和功率开关管到地的回路,电源为电感L 充电,电感电流上升,检测电压Vcs随之升高。 Vcs 大于上电压阈值时,控制电路关断开关管,重复上个周期的动作,这样就完成了对L ED驱动电流的滞环电流控制,使得流过L ED 的驱动电流,也就是电感电流的平均值恒定。

图2 滞流控制模块内部模块

2. 2 滞环比较电压产生电路

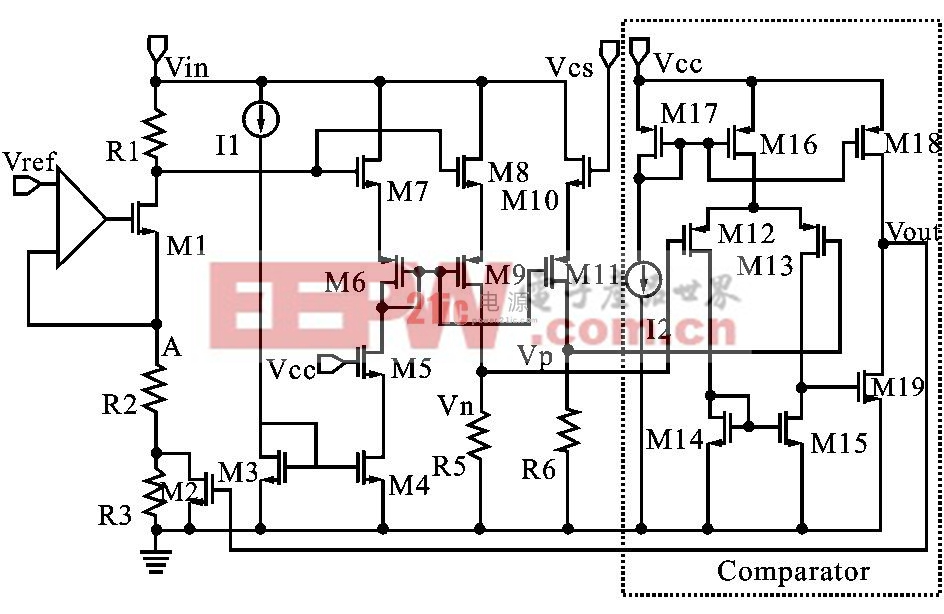

4. 5V~28V 的输入电压经调整转换为5V 的恒定电压Vcc 为后续电路供电。 如图3 所示,A 点电位受运算放大器钳制,将等于参考电压1. 2V ,假设输出V out 为高电平,则M2 导通,流过M1 的电流为IM1 = V ref / R2 ,B 点的电压为V BL = V in - IM1 R1 ;当V out为低电平,M2 截止,流过M1 的电流变为I′M1= V ref / ( R2 + R3 ) ,B 点电压升高为V BH = V in -I′M1 R1 ,所以B 点电压的变化为ΔV B = V BH - V BL= V ref R1 R3/ R2 ( R2 + R3) ,这意味着V out由高电平变成低电平时在B 点产生的一个滞环电压,可见该滞环电压与输入电压无关,只由参考电压V ref和电阻大小决定,通过选择各电阻的阻值便可设定滞环电压的大小。

图3 滞流比较电压产生电路

2. 3 运放实现电路

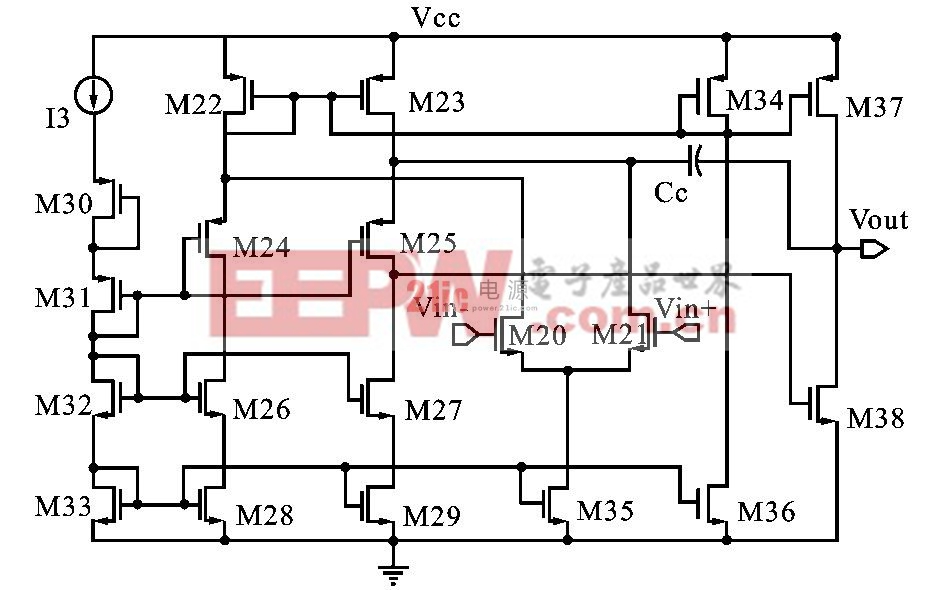

以上分析可知运算放大器起着重要作用,其必须具有较高的增益,才能使A 点电压精确跟随参考电压,从而准确设定B 点电平和滞环电压大小。 另外由于V out的变化频率与系统开关频率相同(系统的最大开关频率约为2MHz) ,使得流过M1 的电流也相同频率在IM1和I′M1之间快速切换,所以运放的单位增益带宽须大于系统的最大开关频率。 设计的运放结构如图4 所示,采用折叠式输入结构,可以获得较大的共模输入电压范围。

由运放的频率特性仿真图5 可知,增益达到84. 266dB ,相位裕度108°,单位增益带宽约12MHz ,满足电路要求。

图4 运放实现电路

图5 运放频率特性仿真

2. 4 平均驱动电流

设定

运放将点A 电位钳位于

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)