序列信号发生器的设计方法及应用实例

时间:04-17

来源:互联网

点击:

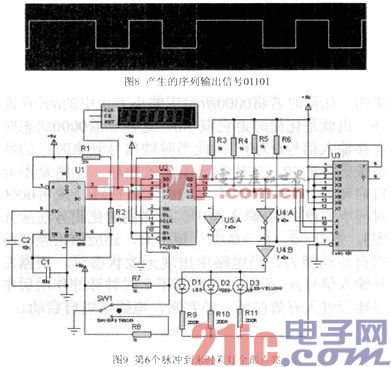

使用这种电路可以驱动一路多个彩灯按照一定的规律亮灭,构成灯光控制器。在图3所示电路的基础上,设计出仿真电路,和理论电路不完全相同。Proteus软件中没有74HCT151芯片的模型,在下图中以74HC151代之。存在用TTL电路驱动CMOS电路的问题,TTL电路输出高电平下限值低于74HC系列输入高电平的下限值,解决办法是在TTL电路的输出端与电源之间接入上拉电阻以提高TTL电路输出的高电平。该电阻阻值不能过小,太小时,TTL门电路输出为低电平时流过三极管的电流过大,容易把器件烧坏;该电阻阻值也不能过大,过大会导致TTL门电路输出为高电平时上拉电阻上压降过大,引起输出高电平值的降低。综合考虑以上两种情况,取上拉电阻为1kΩ。设计的灯光控制器由555定时器构成的时钟脉冲信号产生电路、开关控制电路、移位寄存器、数据选择器以及灯光电路五个部分组成,可以驱动1路3个彩灯。图中Q0为序列信号输出端,驱动彩灯电路。为了使得Q0在驱动彩灯电路时输出高电平不致降低,采用U4:A和U5:A两个反相器串联,以减小该负载电路的驱动电流。开始仿真时,首先把开关掷向上方,S0=1,寄存器置入初始数据0110,然后把开关掷向下方,S0=0,寄存器中的数据按照指定规律移位。3个彩灯同时点亮,同时熄灭。亮灭的规律为:灭亮亮灭亮。彩灯亮灭的速度可由时钟信号CLK的频率控制。图中555定时器构成多谐振荡器产生频率为1Hz的时钟信号,因此彩灯亮和灭所持续的时间均为1s。时钟信号的仿真图如图7,周期为1s,占空比为63.83%。产生的序列输出信号仿真结果如图8所示。当第6个时钟信号到来时,Q0Q1Q2Q3=1101,此时序列信号输出端Q0输出高电平,彩灯全部点亮,电路的仿真结果如图9所示,图中还接入了频率计,显示时钟频率为1Hz。

序列信号发生器的构成方法很多,本文对其进行了详细介绍,结合具体例子给出了设计的全过程。并运用构成的序列信号发生器设计了灯光控制电路,分析和解决了电路设计过程中所遇到的各种问题,用Poteusr软件进行了仿真并分析了输出结果,使所介绍理论设计变成了实际应用。设计的灯光控制电路由集成芯片和门电路组成,电路成本低,具有很强的实用性,有一定的应用价值。

序列信号发生器 移位寄存器 计数器 彩灯控制电路 相关文章:

- 数字钟实验电路的设计与仿真(07-23)

- 计数器在数字电路中的应用(01-17)

- 基于PWM功能的AVR单片机定时-计数器设计(04-23)

- 基于集成计数器的N进制计数器设计与仿真(04-19)

- 基于可编程计数器的时序逻辑电路设计(08-09)

- 基于JK触发器的12归1计数器的设计与实现(06-30)