基于JK触发器的12归1计数器的设计与实现

摘要:触发器是数字电路的基本逻辑单元之一,也是构成各种时序电路的最基本逻辑单元。文中给出了基于JK触发器来设计十二归一计数器的设计和实现方法,并通过EWB软件进行了仿真。

关键词:JK触发器;12归1;计数器;时序电路

O 引言

在现实生活中,任意进制的归一应用都十分广泛。触发器是数字电路中的基本逻辑器件,本文给出了用JK触发器设计实现十二归一计数器的设计方法,该方法也可以扩展到设计实现任意进制的计数器。

1 计数器的基本原理

根据12归l计数器的设计要求,可利用4个JK触发器来实现12归1计数器,其JK触发器的功能表如表1所列,计数状态表如表2所列。

12归1计数器通常有两种功能,即计数和置1,通过分析JK触发器的功能表和计数器状态表,可以看到,要实现计数,也有两种方法,即同步计数和异步计数;而要实现置1,同样也有两种方法,即利用JK触发器的端异步置1和直接利用J、K端同步置1。

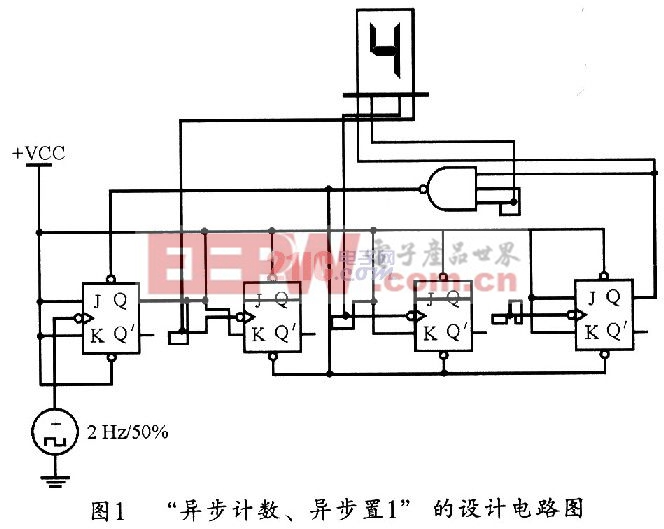

2 异步计数/异步置1法的设计

异步时序电路是指无统一CP,输入时钟脉冲只作用于最低位触发器,各触发器间串行连接,即状态更新逐级进行的一种计数器电路。图1所示就是一种异步计数器的电路图。

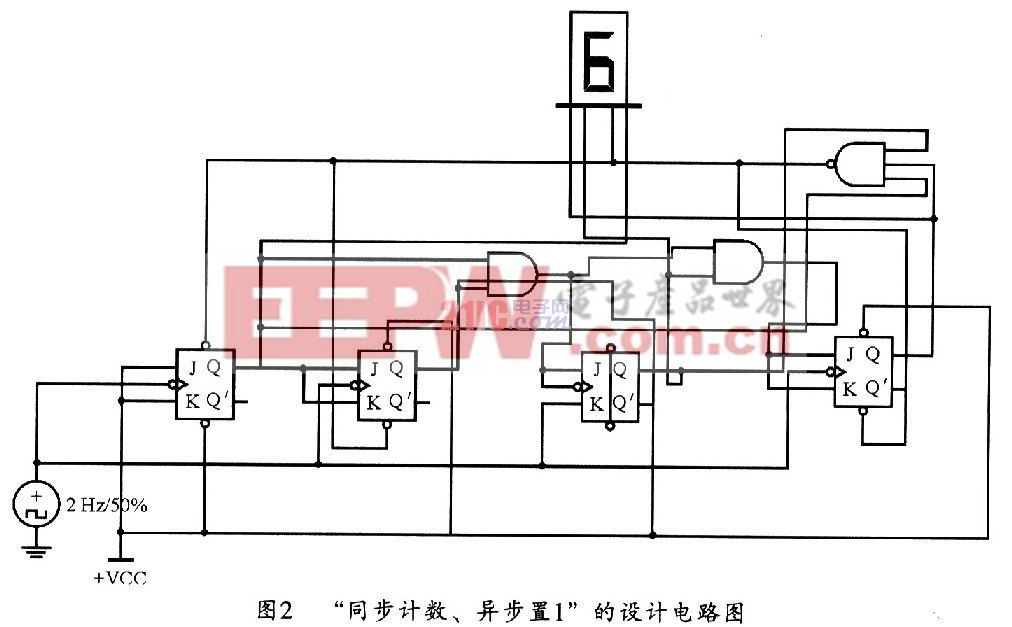

3 同步计数/异步置1法的设计

所谓同步时序计数器,是指有统一的CP、状态更新与CP同步、而且共用的信号源。分析12归1的状态表,可以看出:当低位全部变为1时,高位进位。而将JK触发器的、端置1,即为异步置l,其所设计的同步计数器电路如图2所示。

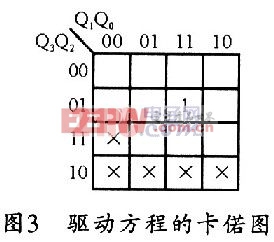

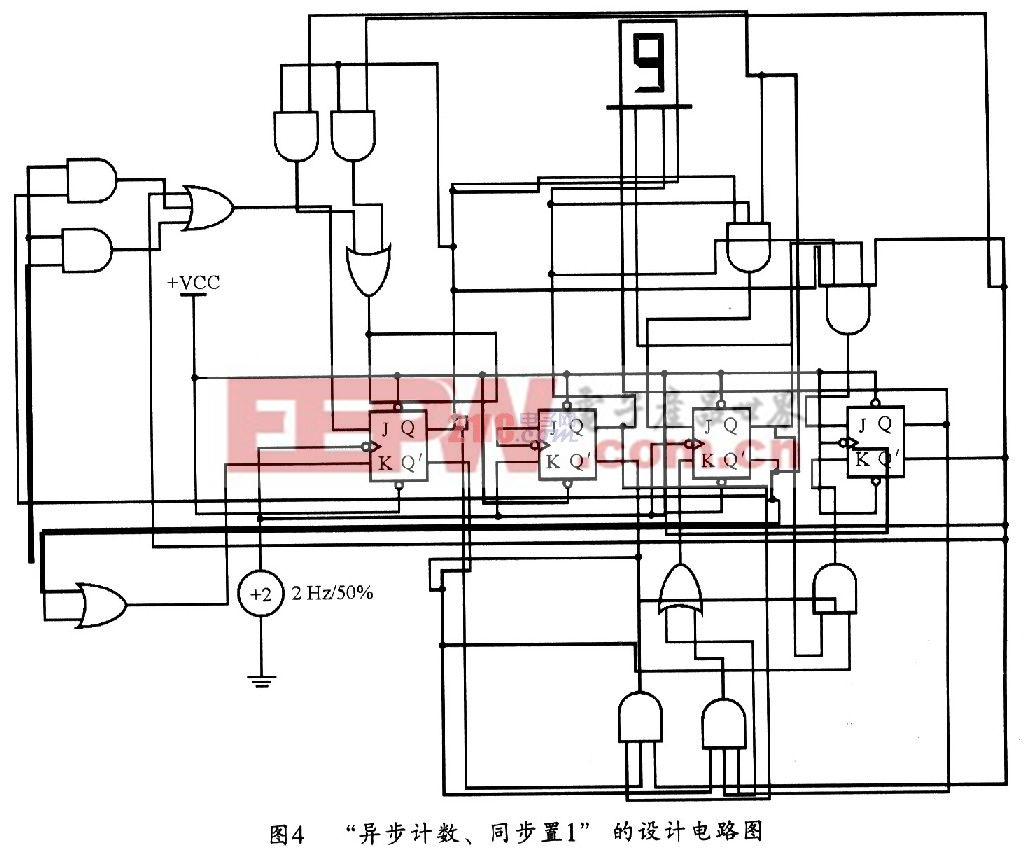

4 同步计数/同步置1法的设计

这种方法的计数器的状态由JK触发器的J、K端直接决定。可根据计数状态表得出J3驱动方程的卡偌图,具体如图3所示。

根据图3所示的卡偌图,可得出如下方程:

根据上述计数方程,再利用逻辑门电路,就可以设计出如图4所示的电路,从而实现十二归一计数器。

5 结束语

同步时序电路和异步时序电路设计的不同之处在于其进位时,同步时序电路由于有统一的时钟脉冲,故其进位时刻为低位全部变为1的时候;而异步时序电路进位时,则依靠低一位由l变到0时向高位提供触发脉冲而使高位改变状态,所以,它的高位时钟端接在低一位的输出端。

同步置1和异步置1的不同之处在于:同步置l要等到脉冲到来时才能翻转,所以,它在计数到12时就可以翻转;而异步置1时,只要满足条件就可以置1,所以,它们的置1时刻是计数到13的时候翻转。

JK触发器是数字电路的基本逻辑记忆单元,利用该触发器可以实现12归1的方法,同时也可以更加深入的理解其功能及同步与异步的区别。

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)