便携式功率分析仪设计-----硬件设计(四)

3.4 FPGA内部电路设计本设计

硬件电路设计采用了1片FPGA,芯片型号为Altera公司的EP1C6Q240C8 。其作用主要分为数据采集控制和频率测量控制两个部分。数据采集控制部分用于实现ARM寄存器基接口的配置,通道控制,数据采集,触发与存储器读写控制等;频率测量控制部分用于利用前端电路已经分频整形的信号对给定门宽进行计数,从而等到该信号的频率值。这里先对数据采样部分的FPGA内部电路进行介绍,频率测量部分的介绍见后章。

数据采集控制部分的FPGA程序主要完成与ARM芯片接口的的配置工作;对寄存器进行译码;控制触发电平,实现触发功能;FIFO读写控制;时钟频率选择;采样时钟合成与控制;寄存器读写操作。以下分别对各部分的功能进行介绍。

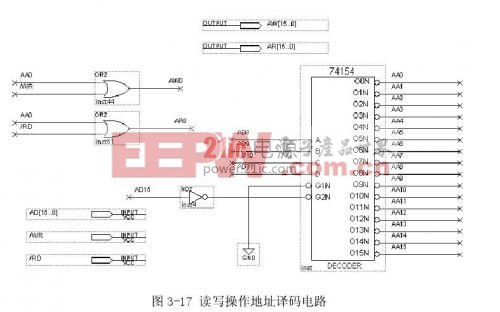

3.4.1地址译码电路及控制信号

模拟通道中的衰减控制信号,以及对FIFO状态的检测信号等,都是由ARM芯片对其数据、地址总线的读写来实现的,这就需要为每个端口分配地址。本设计中,由于是利用LPC2138的两个通用I/O口,模拟读写控制线,由于有独立的读写标志,因此需要4根地址线译码,进行端口读写。

FPGA中与ARM芯片(LPC2138)接口的写操作地址译码电路。其中,/WR为ARM芯片的写使能信号,低有效。当写外部存储器时,/WR信号变为低,而在/WR信号的上升沿时,ARM外部数据、地址总线上的数据都是很稳定的。而且地址总线上的数据比数据总线上的数据先有效。因此,我们可以先对外部地址总线上的数据利用译码器进行译码,等到/WR信号有效时,利用/WR信号的上升沿对外部数据总线上的数据进行锁存,完成对外部存储器的一次写操作。

其中,写寄存器部分主要由74374构成,实现寄存器写操作。送写的数据包括触发字、FIFO状态控制字、DAC控制字、MAX4141通道选择字等控制字。

同样在ARM读操作中,/RD为ARM芯片的输出时钟信号,低有效;当每执行一次读操作时/RD产生一个读时钟信号,同时ARM外部数据总线上的数据在两个读时钟周期内有效。而且地址总线上的数据比数据总线上的数据先有效。因此,我们可以先对外部地址总线上的数据利用译码器进行译码,等到/RD读时钟信号有效时,选通相应的缓冲器,从而完成对外部存储器的一次读操作。

其中,读寄存器部分主要由74244构成,完成寄存器读操作,包括读取FIFO状态字、存储在FIFO中的ADC采集的数据等。

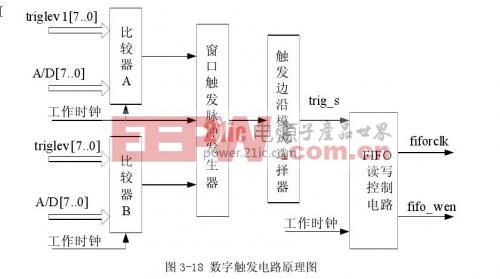

3.4.2数字触发电路

功率测量中,为了得到检波后脉冲的峰值,需要设置触发电平,获得信号的峰值。为了避免毛刺干扰的影响,触发电路设计中选用窗口电路的设计方法。并选用上升沿/下降沿触发。具体触发电平大小的设置,根据于采样得到信号的峰值,如下图3-18所示,触发电路由两个比较器、选择器和触发器等组成。触发电平triglev小于triglev1,构成窗口触发的两个电平。第一路比较器实现触发电平triglev和采样得到的信号值比较,当triglev小于此时的信号值,则第二路经过比较器输出的信号被选通到输出端。第二路比较器实现触发电平triglev1和采样信号比较,当信号高于triglev1则输出端置高。因此,trig_or比较器的输出为采样信号的整形后信号,在后端的trig_s标志为用户提供上升沿/下降沿触发方式的选择。从而实现窗口触发。

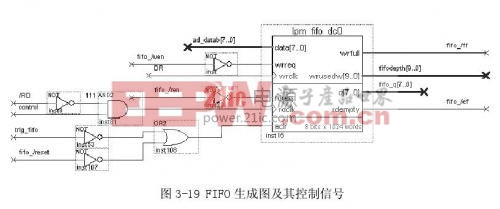

3.4.3数据的存储与控制

A/D采样出来的数据,是随采样时钟和被测信号的变化而变化的,要能够再现被测信号,必须要把每次采集的数据存入缓存器中,这里介绍的FIFO就是一个典型的缓存器。FIFO是一个先进先出的存储器,可同时对存储空间进行读写,没有地址线,第一个读出来的数据是第一个写进去的数据,它有现成的集成芯片。由于EP1C6Q240片内有92160bits的存储空间,因此本设计采用ALTERA公司提供的宏单元库MEGA_LPM中提供的FIFO库文件(LPM_FIFO_DC),将FIFO做在FPGA中。对应AD9480的存储主通道信号采样值的FIFO存储深度设为1024,单位为8bits,生成的FIFO如图3-19所示。

生成的FIFO有一个写使能信号wrreq,一个写时钟信号wrclk,一个读使能信号rdreq,一个读时钟信号rdclk,一个清除端aclr,8bits数据输入端data[7……0]和8bits数据输出端q[];同时还有两个状态端:wrfull(FIFO满)和rdempty(FIFO空),FIFO被写满时wrfull=1,当FIFO被读空时rdempty=1.如图3-19中还使用到一个数据输出端wrusedw[9..0],该端口在每一个FIFO写时钟到来是更新当前FIFO以写入数据数量,这将在做预触发方式时使用。

这里之所以不用一般并行RAM而用FIFO主要有如下两个原因:一方面是它不用地址线,便于电路的连接和控制;更重要的是它可以同时进行读写操作,这样在做预触发功能时是非常方便的。虽然用并行

- 专用于便携设备电源管理的超小型降压转换器(06-29)

- 级联低压差稳压器SMPS(07-12)

- 基于DSP的单相精密电源硬件设计(07-24)

- WiFi 收发器的电源和接地设计(08-12)

- 微安级数控恒流源的设计(08-20)

- 新一代手机电源管理的最佳化挑战(08-30)