一种多通道ARINC429总线收发容错方法的研究

摘要:针对目前ARINC429航空总线的研究情况,采用SoPC技术设计多通道ARINC429总线收发装置,解决了目前使用常规芯片导致的系统复杂,使用不便,价格昂贵的缺点。在需要多通道数据收发的场合中,能够有效降低系统的复杂度,提高系统配置的灵活性。另外,在接收过程中研究了改进型倍频容错数据采集方法,首次将其应用于ARINC429航空总线,实验证明该方法能够大大提高数据接收的准确性和可靠性。

关键词:ARINC429;SoPC;倍频容错;收发装置

在现代飞机上,系统与系统之间,系统与部件之间需要通过总线传输大量信息。ARINC429总线是美国无线电公司制定的一种串行标准,是基于Mark33数字信息传输系统(Digital Information Transfer System,DITS)的单向数据总线标准,是专为航空电子系统通信规定的航空工业标准。它详细规划了航空电子系统中各个电子设备之间及电子设备和系统之间的通信方式。由于其数据资源丰富,数据精度高,现已广泛应用于波音、空客,中小型的直升机中。它规定了航空器电子系统生产厂家对部件、通用设计、结构及试验规范的要求,使那些影响系统互换性和电气特性达到最大程度的标准化。

1 常见的ARINC429协议芯片

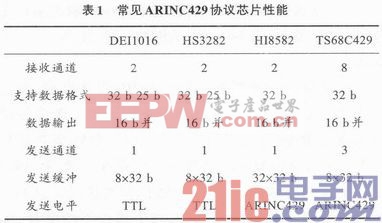

目前常规的ARINC429总线通信的接口设计都是采用DEI1016,HS3282等专用芯片。这些芯片的数据格式固定,数据收发过程中需要额外的数据转换,使用起来不够灵活方便。而且价格昂贵,通道数较少,在实现多通道收发时,不仅增大了系统的体积和复杂度,而且成本极高。

几种常见的ARINC429协议芯片如表1所示。

当前可编程逻辑器件发展迅速,利用SoPC技术设计ARINC429总线接口芯片可以克服以上的不足,同时极大地降低了系统成本,使用更加灵活,可以根据应用环境进行更改相应的系统配置,无需重新设计硬件系统。

2 ARINC429发送模块设计

ARINC429发送模块主要功能是能够按照两种不同速率100 Kb/s和12.5 Kb/s发送标准的32位双极归零码,并在字与字之间自动产生4位空白。

2.1 电平转换电路

由于ARINC429总线采用双极归零码的方式传输数据,对于单根传输线而言,有5 V,0 V,-5 V三种电平。而FPGA只能发出电平是3.3 V和0 V,所以对FPGA产生的信号要加一个电平转换电路,当FPGA输出的两根数据线压差为3.3 V时,转换成一根线为5 V另一根线为-5 V;当压差为0时不变。电平转换电路如图1所示。

2.2 发送模块状态转换

发送模块主要有5个输入端口和3个输出端口,输入端口包括:时钟clk_800 kHz、复位rst_n、发送使能en_tr、待发送数据indata、发送速率speed,输出端口主要包括:发送标志busy_tr、ARINC429总线busa_o和busb_o。

发送模块主要有3个状态:空闲、发送数据、发送时钟。当发送模块处于空闲状态时,只要发送使能信号en_tr为1,则说明有需要发送的信号,跳转至发送数据状态。由于ARINC429总线每一位前半个周期为数据,后半个周期为时钟,所以发送数据和发送时钟这两个状态构成了每一位的发送过程,两个状态不断交替,SoPC系统设计中发送模块状态转移图如图2所示。

3 ARINC429总线接收模块设计

ARINC429总线接收模块,要实现能自动识别两种速率100 Kb/s和12.5 Kb/s,并对数据进行校验。

3.1 电平转换电路

和发送模块类似,接收模块在接收信号之前,也要进行电平转换,将信号转换成FPGA能识别的电平,ARINC429接收模块电平转换电路图如图3所示。

3.2 接收状态转换

接收模块主要有5个输入端口和2个输出端口,输入端口分别为:时钟clk_800khz、复位rst_n、校验方式set_od、ARINC429总线busa和busb,输出端口包括:输出数据outdata、输出使能done_rec。

接收模块主要包括两个状态:空闲和接收。在空闲状态时,ARINC429总线上没有数据传输时,两根线busa和busb都为逻辑“0”,即clk_429=0时,说明有数据到来,转到发送状态。

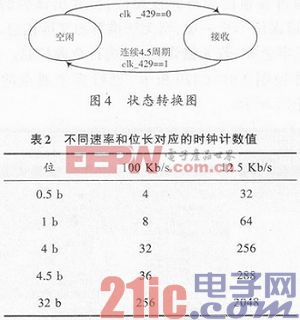

在接收状态时,接收数据并移入移位寄存器,当有连续4个周期busa和busb都为0,即clk_429=1时,表示接收完成,转到空闲状态。然而,在传送最后一位数据时还有半个位周期clk_429=0,所以实际上是连续4.5个位周期如图4所示。由于ARINC429总线有两种发送速率即12.5 Kb/s和100 Kb/s,所以不同速率时的4个周期的时间也不一样,而且传输数据时每一位都有半个位周期是时钟周期,因此需列出不同速率和周期对应的时长。本设计的时钟选取为800 kHz,表2为此时钟下的计数值。

从表2中可以看出,在100 Kb/s速率下4个位周期的计数值为32,而12.5 Kb/s时为256,所以无论任何速率当计数值为32时可认为是当前传输结束。但是,12.5

- NiosⅡ软核处理器的SOPC技术实现数码相框设计(01-16)

- 基于SOPC的通用字符VGA显示电路设计(06-29)

- 基于SoPC的数字示波器设计(04-28)

- 基于NioslI的SOPC系统中lED显示驱动IP核设计(04-21)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)