NiosⅡ软核处理器的SOPC技术实现数码相框设计

本文采用了基于NiosⅡ软核处理器的SOPC技术来实现数码相框的设计,从根本上改变了传统设计方案的不足。NiosⅡ软核嵌入式处理器是Altera公司提供的SOPC解决方案。NiosⅡ是一种可配置的16/32位RISC处理器,它结合丰富的外设、专用指令和硬件加速单元可以低成本地提供极度灵活和功能强大的SOPC系统,开发者可以根据实际需要自行整合。SOPC技术在电子设计上给出了一种同时涉及底层的硬件系统设计和相应的软件设计,在系统优化方面有了前所未有的自由度,使得从多角度、多因素和多结构层面上大幅度优化自己的设计成为可能。当电路有少量改动时,更凸现出其优势,可以延长该产品在市场上的寿命,大大提高多功能数码相框的性能。

1 系统总体架构设计及系统硬件设计

基于NiosⅡ的SOPC嵌入式系统开发,主要由三部分组成:IP库(Nios软核处理器,Avalon总线,外围设备接口等),SOPC Builder开发工具,CNUPro软件编译器。另外,使用NiosⅡ进行嵌入式设计在硬件上必须使用Altera公司的FPGA,本文中的设计使用的是Altera的Cyclone系列芯片的EPlCl2Q240C8芯片。

多功能数码相框主要实现以下功能:能清晰地显示JPEG图片的自动播放及其缩略图式浏览;多区播放或者画中画多种显示方式;图片的即时编辑与裁剪(旋转、美化);具有出色的视听娱乐功能,能播放MP3、MP4音频文件,实时字幕滚动叠加;文件和文件的浏览及其对USB接口和SD卡的支持;多种附加功能时钟,万年历等。

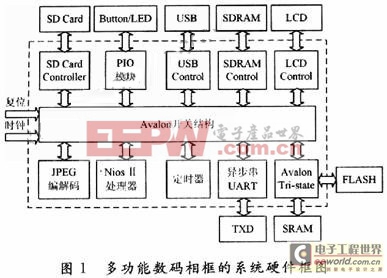

数码相框从CPU的总体结构到局部功能的实现上需要有时钟电路,CPU,RAM及RAM控制器,FLASH及FLASH控制器,SD卡及SD卡控制电路,USB接口及USB接口控制器,液晶屏及液晶显示器驱动电路,DMA控制器,音频驱动及音频控制电路,定时器模块,系统硬件结构图如1所示。

整个设计采用自上而下的设计方法,在SOPCBuilder中搭建系统硬件模块,将所需的各功能模块通过Avalon总线集成,这样系统的稳定性更高。除显示驱动模块、音频控制模块和SD卡控制模块、USB接口控制模块外,其他模块都可以从SOPC Builder中添加IP核构建。

2 LED背光设计

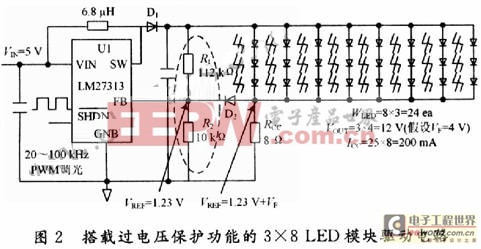

LCD面板是数码相框的主要组成部分,它带有用于背光照明的白光LED,LM27313已被大量用于白光LED BLU解决方案。图2显示了用于8英寸数码相框LCD的白光LED背光电路。

在设计LED背光驱动电路时,LED是电流驱动型器件,为保证光照强度并提高LED的使用寿命,最重要的问题是在LED正向偏置时保持恒流。由于大多数 LED模块是通过一个连接器与主板相连的,LM27313在输出时会因误操作或LED模块受损而开路,误差放大器的负输入端没有信号,输出电压将会无限制地上升,这将造成毁灭性后果,损坏LM27313或输出二极管。为解决这一问题,在图2中加入了一个过电压保护电路。在图2中,电阻器R1和R2通过向误差放大器引脚(FB)馈送输出电压,确保恒定输出电压不会无限上升。

调光控制是指根据客户的喜好控制显示器光照强度。可以通过开/关 LM27313来控制LED的开关,而对LM27313的开关控制可通过在SHDN引脚上应用脉冲宽度调制(PWM)得以实现。脉冲频率必须超过20kHz,低于20 kHz的频率会使电路输出端的多层陶瓷电容器产生波形振荡,从而产生可听噪声。3 LCD典型电源偏置电路设计

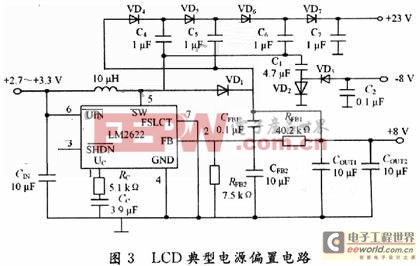

面向LCD平板电源的DC/DC转换中采用了美国国家半导体拥有的最佳的电源解决方案LM2622。在用于数码相框的典型LCD平板显示器中,输入电源电压约为+5.OV。必须提供若干不同的电压,以使显示面板通过该输入电压实现最佳性能,通常情况下需用到升压转换器。可以利用LM2622在+5.0V输入电压下提供若干不同的输出电压。图3中的电路显示了应如何配置LM2622,以提供+8 V,-8 V和+23 V的输出电压,这对于偏置TFT显示器而言是非常方便的。

4 USB接口模块设计

随着通用串行总线(USB)技术的飞速发展和应用领域不断扩大,已经实现了脱离PC而实现USB的点对点的数据传输,嵌入式USB主机能够脱离PC完成 USB的点对点的数据传输。本系统采用的是NiosⅡ+USB接口芯片的方案,USB串行接口可以作为NiosⅡ的一个外设,接口芯片采用的是 Cypress公司生产的SL811HS为主控制器的USB Host/Slave接口芯片。设计的原理方案图如图4所示。

SL811HS 主控制器接口提供8位的数据总线及一些控制信号,如读写、片选等与外部CPU或微控制器进行连接。并且,L811HS接口为外部提供简单的地址线A0,支持可编程I/O或存储器映射设计。通过对SL811HS的读写时序与Avalon总线读写时序的分析,采用了SL811HS中的A0寻址模式与 Avalon总线的“具有一个固定等待的从端口读/写传输”时序,SL811HS的地址和数据均通过D[7..O]分时传输,通过A0(数据/地址选择线)电平的高低加以区分。当A0置为低电平时,D[7..O]上传输的是SL811HS片内寄存器/缓冲区的地址,反之高电平则为数据。在A0模式下,SL8llHS正常的读写操作支持地址自动加1模式,即在此模式下微控制器只设置地址仅仅一次,紧接下一个时钟的读写操作SL811HS内部地址指针将会自动跳到下一个数据位置。nWR,nRD,nCS,nRST分别为写控制线、读控制线、片选线和复位线,均是低电平有效,NiosⅡ通过这几根控制线完成对SL811HS片内缓冲区读写、片选和复位等操作。INTRQ是中断请求信号线。当SL8llHS检测到外设插入、拔出或者数据发送错误、超时、数据溢出等异常情况时,通过将INTRQ置高电平通知NiosⅡ。Avalon总线为用户提供了非常友好的接口,在SL811HS与Avalon总线的接口转换Verilog代码中,只需建立SL81lHS端口与Avalon总线端口的映射关系即可。如图5所示。

SL811HS 主控制器接口提供8位的数据总线及一些控制信号,如读写、片选等与外部CPU或微控制器进行连接。并且,L811HS接口为外部提供简单的地址线A0,支持可编程I/O或存储器映射设计。通过对SL811HS的读写时序与Avalon总线读写时序的分析,采用了SL811HS中的A0寻址模式与 Avalon总线的“具有一个固定等待的从端口读/写传输”时序,SL811HS的地址和数据均通过D[7..O]分时传输,通过A0(数据/地址选择线)电平的高低加以区分。当A0置为低电平时,D[7..O]上传输的是SL811HS片内寄存器/缓冲区的地址,反之高电平则为数据。在A0模式下,SL8llHS正常的读写操作支持地址自动加1模式,即在此模式下微控制器只设置地址仅仅一次,紧接下一个时钟的读写操作SL811HS内部地址指针将会自动跳到下一个数据位置。nWR,nRD,nCS,nRST分别为写控制线、读控制线、片选线和复位线,均是低电平有效,NiosⅡ通过这几根控制线完成对SL811HS片内缓冲区读写、片选和复位等操作。INTRQ是中断请求信号线。当SL8llHS检测到外设插入、拔出或者数据发送错误、超时、数据溢出等异常情况时,通过将INTRQ置高电平通知NiosⅡ。Avalon总线为用户提供了非常友好的接口,在SL811HS与Avalon总线的接口转换Verilog代码中,只需建立SL81lHS端口与Avalon总线端口的映射关系即可。如图5所示。

NiosⅡ软核处理器 SOPC技术 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)