数字电源排序

电源排序是数字电源架构的一个关键部分。在这我们来看看几种设计排序的方法及其结果。特别地,我们将了解一下设计选择在设计过程的后期对灵活性所产生的影响。

电源转换的构件

让我们来看一下自己的电源构件和工具,并了解我们会给自身带来何种类型的麻烦。为简单起见,我们假定拥有一个通用的电源构件(UPB)以及所有常见的“麻烦制造者”(例如:FPGA和微控制器、以及逻辑器件等)。我们的UPB具有一个简单的接口:

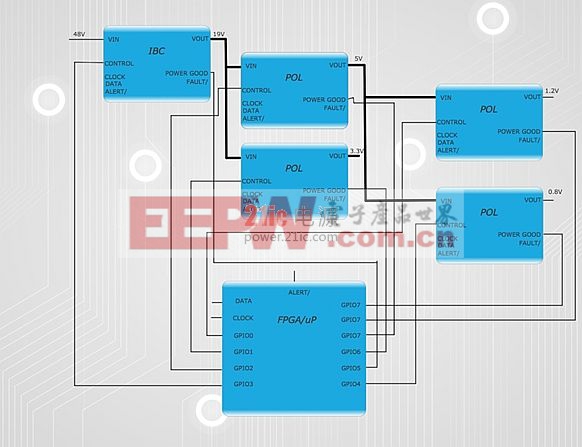

图1:电源构件。

我们简单的电源转换器具有单个VIN/VOUT、一个PMBus接口、一个输入信号(CONTROL)、以及两个输出信号(POWER GOOD和FAULT/)。

CONTROL

CONTROL信号负责输出的接通和关断。其为高电平有效,并具有一个内部上拉电阻器。

POWER GOOD

POWER GOOD信号在输出通电时为高电平,而且它处于有效范围之中。

FAULT/

FAULT/信号为低电平有效,开路漏极,并在电源构件具有某种故障时被置为有效。如果存在某种故障,则ALERT/被置为有效,并且可以通过PMBus读取故障信息。不是所有的电源转换器都将具有一个POWER GOOD和一个FAULT/,我们不需要两者兼备。几乎在每种场合中,FAULT/皆可作为POWER GOOD的“替身”。

设计方案一

现在我们来设计某种方案,这样就可以将之拆解并设计另一种方案,从而一次比一次做得更好。

假设我们有一个系统,此系统具有一个中间总线控制器(IBC)和以下的电源轨:48V、19V、5.0V、3.3V、1.2V、0.8V。

我们决定把这些电源轨构造为一种层级体系。不过,我们需要一种用于上电的不同控制结构。

图2:简单的电源结构。

对于实际的设计,不要担心电源层级体系或逻辑是否正确。要紧的是这种结构“类型”所产生的影响。我们来研究一下其优缺点。

从好的方面来说,不管是在原理上还是对于实现,它都是很简单的。添加LED指示器或者利用一个FPGA或微处理器的GPIO来读取电源良好信息将非常容易。如果出现故障情况,POWER GOOD将让系统知道某个电源轨发生了故障。

从坏的方面来说,假如存在某种故障,而且倘若系统必须关断所有的电源,那么就必须按照与其上电时相同的顺序把它们逐个关断(别无选择)。这意味着,位于最下游的电源轨将由于失去电源而断电,而不是通过其控制引脚来实现断电。

由于没有定时控制,因此将不得不增添额外的电路以在电源轨之间安置延迟。如果在电源轨之间添加一个延迟,则该延迟将仅适用于上电,因为一个馈电电源轨上的电源将在断电时丢失,因而将在POWER GOOD信号可以使其关断之前关断其所依赖的电源轨。

对于这种结构“类型”,如果您出现任何错误,那么将必需进行PCB的重新布局,而且在等待的过程中,您将被迫修改设计中的导线(别无选择),或者去“享受”漫长的休息时间。

设计方案二

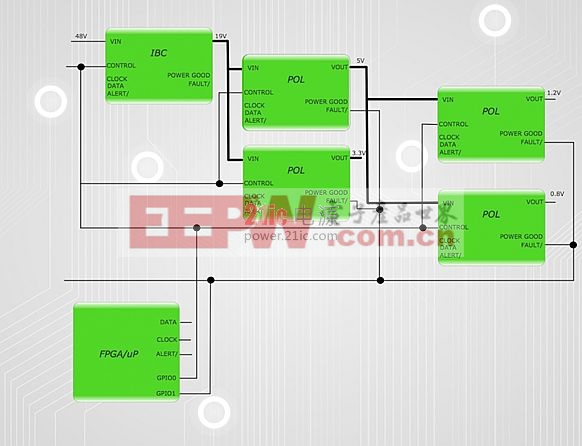

如果我们将逻辑电路集中管理,就能做得更好。一个可编程器件(例如:FPGA或微处理器)能够管理所有的逻辑电路。

通过把所有的逻辑线路均排布至GPIO,控制器即可实现针对排序顺序(接通和关断)以及定时操作的全面控制。其可在希望改变Verilog或C代码时随时变更。我已经标示了控制器上的PMBus(但并未绘出所有的接线),而利用PMBus,控制器现在还能控制电平和故障行为特性。

图3:采用控制器的电源结构。

就优点而言,该设计具有灵活性,而且您不会陷入焦头烂额的困境。假如您在控制结构中出错,无需重新布局即可加以修复。

就缺点来说,您不得不改变Verilog或C,而且有可能需对固件重新实施测试和鉴定。另外,这种设计还必需进行大量的布线。每个POL需要5根控制线,而且它们单独地排布至控制器。假设我们有一个20轨系统,由于PMBus的原因,将需要42个GPIO引脚。

所以,这种设计虽然具有灵活性,但需要很多的GPIO并占用大量的PCB面积资源。

设计方案三

当与PMBus及智能数字电源POL组合时,我们可以采用开路漏极控制的特性来简化控制器。

所有的CONTROL引脚连接在一起,而所有的FAULT/引脚连接在一起。这意味着一个20轨系统只需要5根接线,从而使IO引脚的数目减少了8倍。

图4:简化的控制器。

让我们来看看这是怎样奏效的。CONTROL引脚为高电平有效。其受控于GPIO0(这被设定为“开路漏极”)。由于CONTROL引脚为开路漏极,这意味着POL也可将其拉至低电平。

当POL复位时,它将把CONTROL引脚拉至低电平,直到其准备好响应一个外部信号为止。这意味着倘若控制器速度过快,则不会有任何一个POL接通(直到它们全部正确复位为止),而且系统何时上电取决于最慢的POL复位。如果控制器速度较慢,则其在释放CONTROL线时负

- 控制系统中常见的几种地线详解(10-13)

- 真正的数字电源是什么?(05-12)

- 如何利用智能MOSFET提升数字电源性能?(12-09)

- 解析数字电源与模拟电源的优劣(12-08)

- 基于数字电源控制器UCD3138的一种新的输入电流检测方法(二)(12-08)

- 数字电源与模拟电源的发展趋势(12-08)