采用增益提高技术的两级放大器的设计

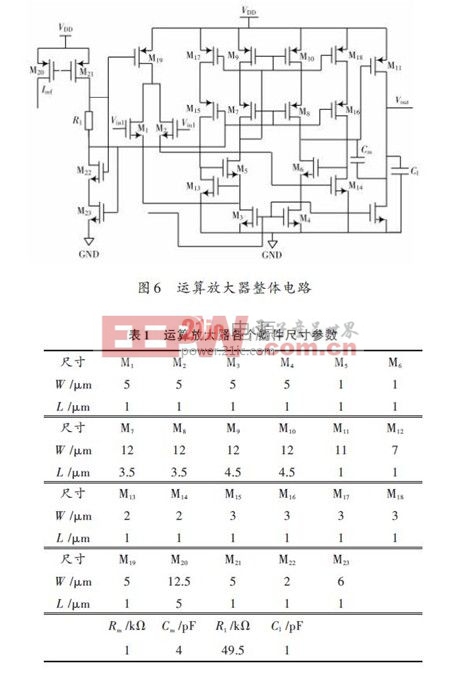

图6 为本文所设计的运算放大器的整体电路.各个端口定义为:VDD 为工作电压;GND 为电源地;Vin1 为正相输入端;Vin2 为反相输入端;Vout 为输出端;电阻Rm=1 kΩ,电容Cm=4 pF.Iref 为10 μA 的电流源.为了使在闭环电路中反馈运算放大器的输入端的信号幅度和相位不使该信号在环路中产生振荡,在电路的增益提高级和输出级之间添加了密勒补偿电容和补偿电阻.电路的第一级为采用增益提高技术的共源共栅结构,其输出电阻很大,所以主极点在第一级的输出端.采用密勒补偿电容Cm 把主极点向低频移动,非主极点向高频移动来实现极点分离.采用补偿电阻Rm 来改善零点的频率,从而使运算放大器达到稳定.表1为整个运算放大器的各个管子的尺寸参数.

3 电路仿真结果

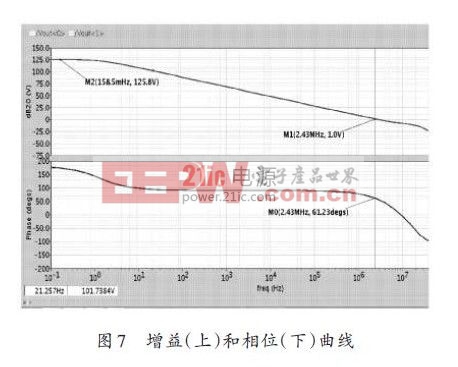

采用Cadence公司的仿真工具spectre,仿真模型采用Chartered 0.35 μm,3.3 V 工艺BSIM3V3 模型对所设计的运算放大器进行了仿真.增益和相位仿真结果如图7所示,增益为125.8 dB,增益带宽积为2.43 MHz,相位裕度为61.2°.

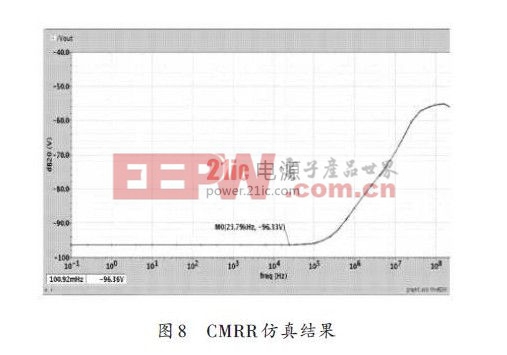

在仿真过程中,对CMRR 的仿真采用了简化的仿真办法,仿真的是实际数据的倒数.从图8 中可以看出,低频共模抑制比(CMRR)为96.3 dB.

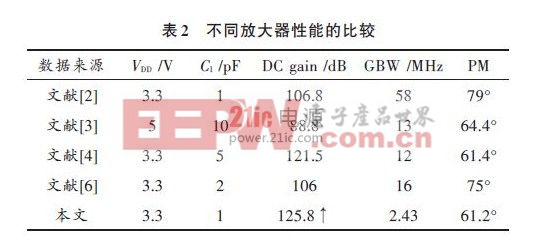

表2 为所设计的运算放大器与其他两级运算放大器性能的比较.

4 结论

本文采用Cadence公司的仿真工具spectre,仿真模型采用chartered 0.35 μm 工艺对所设计的采用增益提高技术的折叠式共源共栅两级放大器进行了DC,AC及瞬态分析,仿真结果表明,本文所设计的两级运算放大器具有125.8 dB的直流开环增益,与采用类似技术的其他放大器相比,其增益可达到最大.在1 pF的负载电容条件下,运放的单位增益带宽积为2.43 MHz,相位裕度为61.2°,共模抑制比96.3 dB,使电路达到了稳定状态,并且模拟结果达到了预期的效果.

- 用于电压或电流调节的新调节器架构(07-19)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 适合高效能模拟应用的线性电压稳压器(07-19)

- 低功耗嵌入式实现的方方面面(04-30)

- 用于低成本高效率离线LED驱动器的初级端调节技术(05-14)

- 开关模式LED驱动器的调光技术(10-20)