基于可逆逻辑电路的脉冲分配器设计

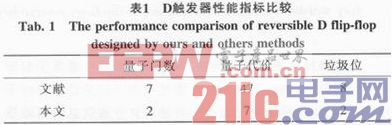

由图3(a)所示,当C输入为0时,输出Q保持不变,当C输入为1时,输出Q和D的信号相同。将图3(a)中的电路封装成图3(b)所示的模块。本文设计的可逆D触发器(图3)的性能指标和文献中设计的可逆D触发器比较如表1所示。

由表1可以看出本文设计的量子可逆D触发器比文献所用的量子门数减少了5个,量子代价减少了40,垃圾位减少了6个。在设计多位脉冲分配器时,量子门数、量子代价和垃圾位会有明显降低。

图2所示的计数器是扭环计数器,根据设计原则,将计数器中的触发器替换成可逆D触发器,从而设计出可逆扭环计数器。如图4所示。

可逆扭环计数器和译码器共同组成脉冲分配器,译码器主要由与门构成,而可逆逻辑电路中没有相应的与门,必须用常用可逆逻辑门构造,Toffoli门可以完成此功能,两输入的与门要三输入的Toffoli门构成。另外,不可逆脉冲分配器的扇入扇出需要进行重新设计,每个扇入或者扇出的节点要用Fevnman门对信号进行复制。

结合图2所示的可逆扭环计数器和图4所示的可逆扭环计数器,构建的量子可逆脉冲分配器如图5所示。

3 仿真结果分析和物理实现

由图5可以看出,本文所设计的量子可逆脉冲分配器所用量子门数为32,量子代价为96,垃圾位24。

可逆脉冲分配器的结构在实验中用VHDL进行描述封装,代码通过Xilinx ISE9.li下载到Spanan-6 LX FPGA芯片上进行运行仿真,目标器件为XC6SLX9。可逆脉冲分配器的仿真结果如图6所示。

由图6可以看出,本文设计的可逆脉冲分配器可以实现8节拍脉冲输出功能,并且无冒险与竞争现象。

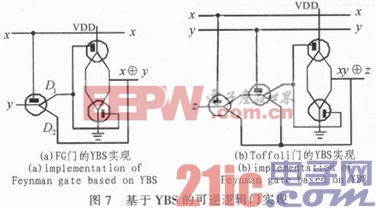

目前已经提出了多种可逆逻辑电路的物理构建方法,如利用低功耗CMOS晶体管构建可逆逻辑门,而利用电子波导Y-分支开关)Y-Branch Switch YBS)构建可逆逻辑门可以用更少的能量改变开关状态,它的打开和关闭是通过改变电子传输两个方向中的一个,而不是切换当前的开关,在正常情况下,YBS的一次开关动作大约散失0.6meV的热量,一个信息位丢失所损耗的能量为KT*Ln2,大约等价为18meV,利用YBS作为基本单元构建可逆逻辑门会更加节能。如图7所示,为利用YBS作为基本单元构建的FG门和Toffoli门,由于所有的可逆逻辑电路都能有Toffo li门实现,所以可逆脉冲分配器可以由图7所示的可逆逻辑门设计物理电路。

4 结论

文中提出了一种可逆时序电路的设计方法,以不可逆脉冲分配器为例,将其转化为可逆脉冲分配器,分析了所设计的可逆脉冲发生器的有关性能指标并对其功能进行了仿真。另外提出了可逆脉冲分配器的物理实现方法。结果表明,设计的可逆脉冲分配器能完成脉冲输出的功能。此方法还可以用于其它可逆时序逻辑电路的设计。

可逆逻辑电路 D触发器 可逆脉冲分配器 电子波导Y-分支开关 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)