可编程能力使高速ADC实现更多特性并进行性能折衷

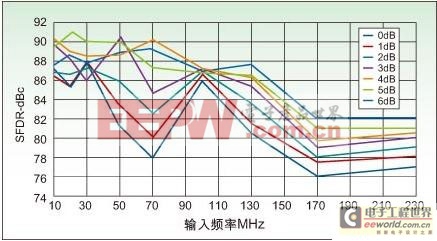

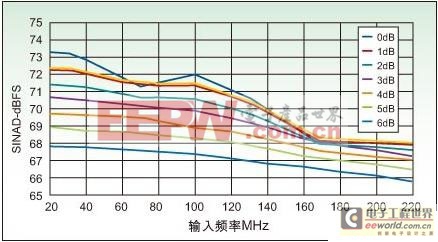

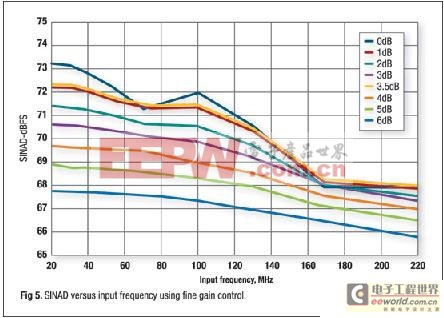

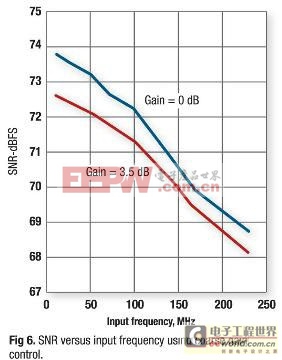

和费用。要看清楚LVDS接收器件要求的电压值。因为每块板都是不同的,你可能需要对ADC编程以便调整LVDS输出电平。这可以在电路板信号丢失被表征和考虑后,在LVDS接收端来维持允许的范围。 内置测试模型 ADS*5提供了多种内置的测试模型,可以在没有模拟输入源的时候使用。这些模型可以在初始电路板调试时用来考察ADC和FPGA之间的时序关系,以便确定FPGA接口处正确的时钟与数据关系。这能确保有良好的时序(时序通常可以在FPGA LVDS输入信号中调整)。 与提供模拟信号相比,使用内置练习模型的一个好处是模型具有一致性,因此可以排除模拟源带来的任何误差问题,使实验具有可重复性,也更容易建立。练习模型也可以在电路板制造与测试过程中用作电路板功能测试的一部分。 信号增益、SNR和SFDR 可编程性不仅仅能解决板级互连问题,一些特性还可以用来实现系统性能折衷。举例来说,ADS*5也有内部模拟输入信号增益功能,允许牺牲SNR来提高SFDR,或只是降低模拟输入幅度。 ADS*5既有粗略增益调整也有精细增益调整。在这两种情况下,模拟输入电压值必须至少要减去ADC中所选取的增益值。这样可以保持ADC的输入电压范围,避免让数字输出字饱和或削减。因此,如果你想使用ADC中的增益设置进行开发,最好要在ADC之前的模拟电路中就计划减少板级模拟输入信号的电平。 从图3和图4可以看出,折衷在输入信号电平和使用两种不同增益调整方法导致的失真(或这里特指的SFDR)之间是显而易见的。这个特性可用来获得多重对象。对于能利用数字抽取技术恢复SNR的窄带系统来说,根据涉及的输入频率,可以通过降低转换器中的SNR来改善SFDR。 图3:使用精细增益控制时SFDR与输入频率的对比。 图4:使用粗略增益控制时SFDR与输入频率的对比 另外,通过允许更小的输入信号进入ADC,同时仍保持来自ADC的全刻度代码,驱动ADC的模拟电路就可能改善失真,并为放大器和ADC整合电路创建更好的SFDR。 可以在创建原型的阶段就使用这个特性,以便确定输入信号电平的最佳组合,从而无需设计多块电路板就能取得最佳的系统失真。可以在系统中动态地进行增益调整,并一道使用自动增益控制(AGC)来恢复尽可能多的动态范围。还可以通过一个封装引脚实现粗略的3.5dB增益设置,以便用于那些没有SPI但想要调整ADC增益的应用,附加的内部寄存器子集也是如此。 图5和图6给出了信号-噪声及失真比(SINAD),以及与A/D转换器的内部增益设置有关的SNR减少的情况。 图5:使用精细增益控制时SINAD与输入频率的对比 图6:使用粗略增益控制时SNR与输入频率的对比 由于高速A/D转换器的可编程性越来越强,它们对用户的友好程度也越来越高。对那些厌烦SPI方法或编程的传统模拟硬件设计师来说,该ADC仍可以使用默认的设置,直接简单的忽略掉其可编程特性。 高速ADC是模拟和数字硬件之间的桥梁,它经常由全数字或全模拟硬件设计师负责。此时,数字硬件设计师更容易接受其可编程特性,但它也可以帮助那些无法正确建立数字时序或信号完整性的模拟硬件设计师节省宝贵的时间。

- S3C2440A嵌入式手持终端电源管理系统设计(01-11)

- 基于CAN通信的电源监控系统的设计(04-06)

- 基于MSP430单片机的电源监控管理系统(04-20)

- 适用于全球交流电源的单节锂离子电池充电器设计(06-07)

- GPIB芯片TNT4882在多路程控电源中的应用(06-08)

- AD7656的原理及在继电保护产品中的应用(06-18)