基于FPGA的TDICCD8091 驱动时序电路设计

时间:11-05

来源:互联网

点击:

流程图如图4所示。程序总共由7个模块组成:输入同步时钟模块产生频率20 MHz的主时钟CLK,CLK 通过分频模块产生频率36 kHz 的CLK1 和频率5 MHz 的CLK2;信号控制模块在主时钟CLK 的同步作用下分别产生控制信号VClr、VSHClr 和HClr;输入处理模块对输入主时钟CLK做去抖动处理后输出时钟信号CLK0;V 信号产生模块输出光积分区域行转移所需的12 kHz 占空比为50%的三相时钟信号V1、V2、V3;VHS信号产生模块输出12 kHz占空比小于5%的移位时钟信号VHS1、VHS2、VHS3;H信号产生模块输出水平移位读出区域所需的20 MHz占空比50%的四相时钟信号H1、H2、H3、H4,以及FOG读出时钟信号和RG复位脉冲信号。

3.2 时序仿真结果

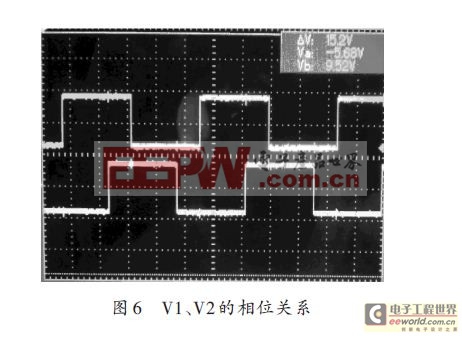

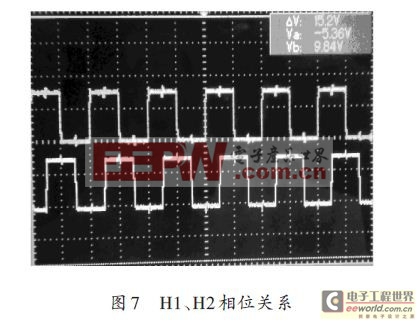

时序设计采用Altera公司的Quartus Ⅱ作为开发平台,EP3C25Q240为硬件平台。总的时序仿真结果如图5所示,结果表明所有仿真信号满足2.2节中的信号要求;图6为FPGA上测得V1、V2的相位关系,图7为FPGA上测得H1、H2相位关系,结果表明相位关系正确,能够保证每个时刻至少有一个高电平和一个低电平,保证像元电荷的正常读出。

4 结语

时序在硬件电路中成功驱动了TDICCD8091工作,验证了软硬件的正确性和准确性。程序设计利用同步时钟控制全局电路的思想,避免竞争与冒险,提高了程序的可靠性;采用模块化设计思想提高程序的可重用性、可测试性、可读性及可维护性;状态机的设计方法提高了程序运行的稳定性。

FPGA TDICCD8091 驱动时序 相关文章:

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 适合高效能模拟应用的线性电压稳压器(07-19)

- TPS54350在信号处理系统中的应用(06-09)

- 基于FPGA的三相PWM发生器(06-23)

- 嵌入式 POL DC/DC 转换器设计(07-22)

- 电源管理与转换的整合可简化电源系统设计(07-24)