控制EMC的三个有效角度

时钟速度的提升加上高频率总线以及更高的接口数据速率使得PC电路板设计的挑战性显着提高。工程师必须超越板上实际逻辑的设计,还要考虑其它可能影响电路的因素,包括电路板的尺寸、环境噪声、功耗和电磁兼容性(EMC)等。硬件工程师应在PC电路板设计阶段解决EMC问题,确保系统不会受到EMC故障的影响。

良好的接地设计

低电感接地系统是最大限度减少EMC问题的最重要因素。最大限度地增加PC电路板上的接地面积可降低系统接地电感,进而减少电磁辐射和串扰。串扰可存在于电路板上的任何两条布线之间,取决于互电感和互电容,与布线之间的距离、边缘速率和布线阻抗成正比。

在数字系统中,互电感产生的串扰通常大于互电容产生的串扰。通过增加布线之间的间距或减少到接地层的距离可降低互电感。

信号连接到地的方法各种各样。组件随机连接到接地点的电路板设计会生成高接地电感,并引发不可避免的EMC问题。我们建议采用全铺地层,这能在电流返回源极时最大限度地减小阻抗,不过接地层还需要专用的PC电路板层,这对于双层电路板而言或许是不现实的。

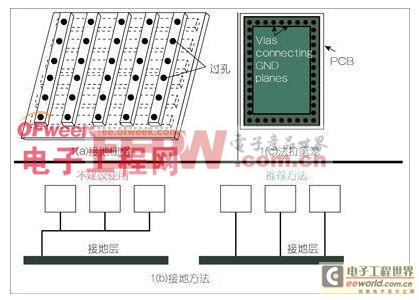

因此,我们建议设计人员采用接地栅格,如图1a所示。在此情况下,接地的电感取决于栅格之间的间距。

此外,信号返回系统接地的方式也很重要。信号路径如果较长,就会产生接地回路,进而形成天线并辐射能量。因此,所有将电流带回源极的布线都应选择最短路径,而且应直接到接地层。

图示:三种接地方法

如果不能采用专用的接地层,则可使用接地栅格代替(1a)。连接所有不同接地并将它们连接到接地层的做法并不可取,因为这不但会增加电流回路的大小,而且会增加接地反弹的可能性(1b)。让接地与电路板的完整边缘拼接在一起,形成法拉第笼,从而不会把任何信号路由到界限之外(图1c),这种方法能把电路板的辐射限制在界限以内区域,避免外部辐射干扰电路板上的信号。 连接所有不同接地并将它们连接到接地层的做法并不可取,这不但会增加电流回路的大小,而且会增加接地反弹的可能性。图1b给出了将组件连接到接地层的推荐方法。

减少EMC相关的问题还有一个好方法,就是让接地与电路板的完整边缘拼接在一起,形成法拉第笼,从而不会把任何信号路由到界限之外(图1c)。这种方法能把电路板的辐射限制在界限以内区域,避免外部辐射干扰电路板上的信号。

从EMC的角度来看,各层的适当安排也很重要。如果使用的层数超过两层,那么要用一个完整的层作为接地层。如果采用四层电路板,那么接地层下面的一层应作为电源层。必须注意接地层的位置应在高频信号布线和电源层之间。如果使用双层电路板,完整的接地层不可能实现,那么可采用接地栅格。如果不使用单独的电源层,那么接地布线应与电源布线平行,以确保电源清洁。

布局指南

为了让设计免受EMC的影响,电路板上的组件必须根据功能进行分类(模拟、数字、电源部分、低速电路、高速电路等)。每类的布线应在指定区域内。在子系统的边界处应使用滤波器。

应对数字电路问题时,必须特别注意时钟和其它高速信号。连接这种信号的布线应尽可能短,而且应与接地层相邻,从而保持辐射和串扰可以得到控制。

对于这种信号而言,工程师必须避免在电路板边缘或附近连接器处使用过孔或布线。此外,信号还必须远离电源层,因为这会引起电源层噪声。传输差分信号的布线应尽量靠近彼此,从而可最有效地发挥磁场消除功能。

从源极向器件传输时钟信号的布线应有匹配终端,只要阻抗不匹配,就会出现信号反射问题。如果不注意处理反射信号问题,大量能量就会辐射出去。不同形式的有效终端包括源点、端点和AC终端等。

对于面向振荡器的布线而言,除接地外的其它布线不应与振荡器或其布线平行或在其下方运行。此外,晶体也应靠近所需的芯片。

由于返回电流总沿着最低电抗的路径走,因此传输电流的接地布线应靠近传输相关信号的布线,从而保持电流回路尽可能的短。

传输模拟信号的布线应与高速或开关信号分开,而且必须用接地信号进行保护。必须始终采用低通滤波器来去除周边模拟布线耦合的高频噪声。

此外,模拟和数字子系统的接地层不能共享。 电路板外的注意事项

电源上的任何噪声都可能影响工作中的器件功能。通常来说,耦合在电源上的噪声频率高,因此需要旁路电容或去耦电容进行滤波。

去耦电容为电源层到接地的高频电流提供低阻抗路径。电 流流经路径至接地,这个路径形成了接地回路。

该路径应保持尽可能低的电平,为此可让去耦电容尽可能地靠近IC。

大型接地回路增加了辐射,可能是EMC故障的潜在来源。频率越高,理想电容的电抗越

- 控制系统中常见的几种地线详解(10-13)

- 嵌入式碟式太阳能热发电控制器研制与应用(06-28)

- 基于金升阳电源的智能窗帘控制器的设计(03-20)

- 控制电源开关技术是影响电源稳定的一大因素(12-09)

- 基于ATmega16 的电液伺服阀反馈控制器设计方案(12-09)

- 基于单片机的电梯控制系统的应用设计(12-09)