用于高压、高容量电池系统的低成本 isoSPI 耦合电路

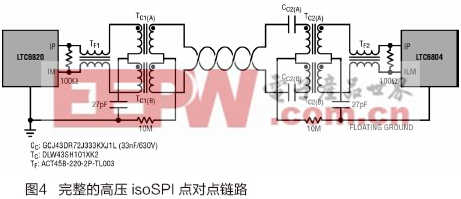

非常有益的 CMC 滤波部分 (采用标准 LAN 组件时,这部分是集成在内的),所以图 4 电路包括一个建议采用的分立式组件,以保留滤波功能。耦合电容器是 10nF 至 33nF 的高质量组件,占板面积为 1812 SMT (额定值为 630V 或 1kV)。这里我们假定,LTC6820 以机架地电位工作,以使双绞线的偏置处于安全水平。

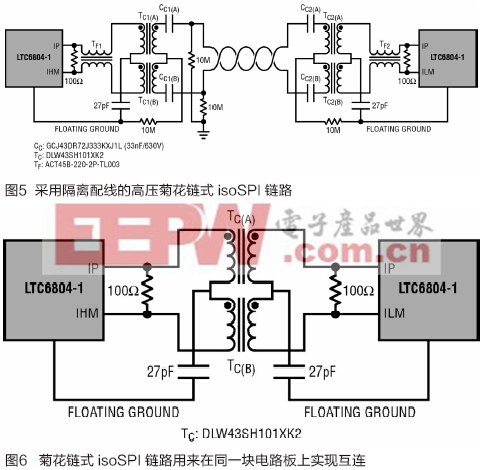

当双绞线对的两个端子都处于浮置地电位时,如同菊花链式连接的 LTC6804-1 模块之间的链路那样,就可以在链路的两个端子上使用电容器,线对本身也可以通过连接到每条线上的高阻值电阻器偏置到“地”电位,如图 5 所示。因为图中电容器是串联的,那么建议至少使用 22nF 电容器 (图中所示为 33nF/630V)。

在同一块电路板上以菊花链方式连接的 LTC6804-1 之间的链路不需要任何电容器耦合,因为其电位通常 <50V,而且由于没有电缆,进入的噪声小得多,所以常常仅需要单个变压器 (图 6)。

高压布局

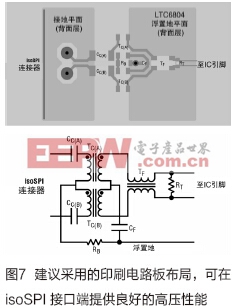

印刷电路板布局应该跨主要电解质势垒 (即电容器) 设置很宽的隔离间隔。图 7 显示了一种组件布局实例,图中电路可提供良好的高压性能,蓝色区域代表机架地 (左边具备双绞线连接器) 和 IC 公共接口 (右边)。

请注意,变压器必须承受 HV 瞬态电位,因此图中也用 1206 大小的偏置电阻器保持空隙。HF 去耦电容器和阻抗终端电阻器可以是小型组件 (如图所示为 0602 大小)。

另一种避免跨 HV 势垒产生漏电流的良好做法是,在 HV 组件 (跨地线之间“缝隙”的组件) 区域抑制阻焊层。这为有效冲洗组件下方的剩余焊剂提供了方便,并避免湿气滞留在多孔阻焊层中。

需要特殊考虑的 isoSPI 总线问题

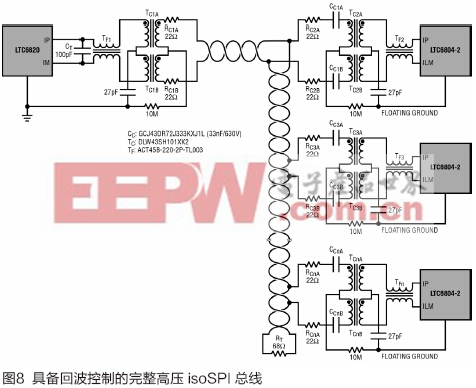

前述电路适用于点对点 isoSPI 链路,但是提供高压解决方案时需要应对的重要问题之一是连接到总线的可寻址 LTC6804-2,该器件的双绞线链路通过每一个“抽头”连接点,如图 8 所示。总线应用对所有变压器都有高压要求,因为同一个双绞线电位必须与浮置电池组的任何电压接口。

与前述相同,这里也用 CMC 和 AC 耦合电容器增强绝缘性,但是我们建议采用略有不同的耦合电路,以衰减大量反射信号,为通信器件提供一致的波形,而不论这些器件在网络中的物理位置。不同之处有 3 种:

LTC6820 终端变为 100pF 电容器 (CT)。

远端终端仅用于运行中的总线 (RT),并设定为 68Ω (任何 LTC6804-2 都没有终端)。

所有总线连接都采用 22Ω 耦合电阻器 (RC),以对杂散容性负载去耦。

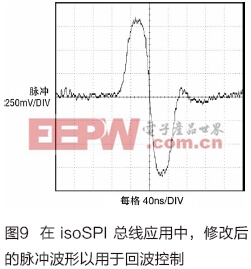

这些差别都显示在图 8 所示电路中,该电路再次假设 LTC6820 以安全的“大地”电位工作。修改后的波形是带限的,以控制反射信号引起的失真,因此 IC 引脚处接收到的脉冲看似更加圆滑,如图 9 所示,不过 isoSPI 脉冲鉴别器电路可以很好地运用这种修改后的波形,支持总共提供 16 个地址的总线。视给定系统中遇到的实际损耗的不同而不同,也许有必要降低脉冲检测门限,以实现最佳工作状态 (将门限设置为差分信号峰值的 40% 至 50%)。

请注意,就地址数量少于等于 5 个的网络而言,信号反射一般不是重要的问题,因此可以保留标准电阻性终端 (即在图 8 中的 CTERM 和 RTERM 位置放置 100Ω 电阻器,而 RC 则省略掉)。

电池 isoSPI 耦合电容器 CMC 变压器 201501 相关文章:

- 电池管理系统故障分析方法及案例(07-05)

- 紧凑型太阳能电池板利用创新性能量收集技术(03-24)

- 基于LTC6802 的电池组监控平台的电路设计(12-09)

- 从原因到措施 教你有效防止电池接反(12-09)

- 无线充电设计必知:通透了解锂电池技术 (12-09)

- 修复电动车蓄电池的电路设计(12-09)