三相SPWM波形发生器的设计与仿真

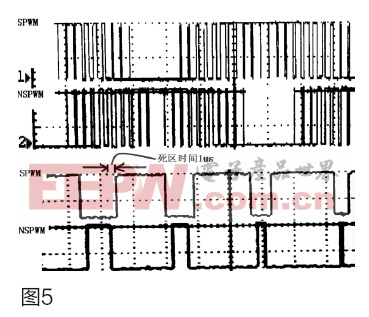

摘要:本文提出了一种采用VHDL硬件描述语言设计新型三相正弦脉宽调制(SPWM)波形发生器的方法。该方法以直接数字频率合成技术(DDS)为核心产生三相SPWM信号。并且利用VHDL设计了死区时间可调的死区时间控制器,解决了传统的模块电路等待方法很难产生带精确死区时间控制的SPWM信号的问题。该方法在Quartus II 9.1环境平台下进行了仿真验证,并将设计程序下载到DE2-70实验板进行实验测试,用示波器测试得到了死区时间可控制的SPWM波形。

引言

三相正弦脉宽调制(SPWM)技术在三相逆变电源系统、交流电机调速系统等领域有着广泛的应用[1] ,并且发挥着核心的作用。SPWM发生器是应用系统设计中的一个难点,目前SPWM波形发生器的设计方法有以下几种:(1)采用模拟电路的方法,用分立元件构成三角波、正弦波信号发生器,再通过LM311等比较器进行自然采样后输出SPWM波形。该方法对元件参数稳定性和电路可靠性要求过高,且输出信号的精度不高。(2)采用专门的SPWM波形发生器集成电路芯片,如SLE4520、SA4828等[2],但这些专用芯片的功能单一,使用不灵活。(3)随着数字芯片的发展,复杂可编程逻辑器件(CPLD)、现场可编程门阵列(FPGA)等器件得到广泛的应用。因此设计基于CPLD/FPGA器件的波形发生器是目前流行的方法[3] 。在SPWM信号发生器的设计中,产生死区时间可任意调节的SPWM信号一直是一个难点。本文利用VHDL语言设计了死区时间控制器,使得输出的两路SPWM信号的死区时间可以任意调节。本文在Quartus II 9.1平台下,采用VHDL语言与DDS技术相结合设计了一种带死区时间控制器的三相SPWM波形发生器,并在DE2-70实验平台下进行了验证。

1 方案设计

采用三角波为载波,对正弦波进行自然采样比较的方法输出SPWM,其采样的原理如图1所示。

本文设计思想为在FPGA/CPLD内存中分别存储了离散的三角波数据、正弦波数据,再利用DDS技术输出三角波数据和正弦波数据,设计一个数据比较器对以上两种波形数据进行实时比较,如果正弦波数据大于三角波数据,SPWM信号输出高电平,反之则输出低电平。根据以上原理,利用DDS技术产生相位差为120o的三相正弦信号分别与三角波信号进行比较,就能输出三相SPWM波形。

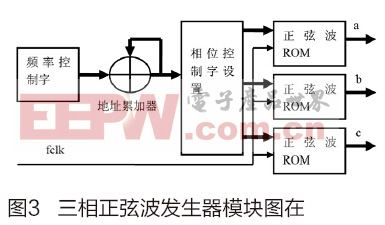

系统的总体框图如图2所示。信号a、b、c为三相正弦波数据,分别与信号d三角波数据进行比较后输出sa、sb、sc为三相SPWM波,再经过死区时间控制器后,最终得到6路SPWM波形输出。其中sa与nsa波形为反向,sb与nsb波形为反向,sc与nsc波形为反向。

2 三相正弦波发生器模块

三相正弦波发生模块如图3所示,该模块根据传统的DDS模块框图进行优化与改进。其原理是由时钟信号fclk控制累加器模块按顺序生成ROM的地址,将存储在ROM中的正弦波形数据逐个输出。

本设计中地址累加器模块地址宽度N为二进制16位,该累加器主要完成频率控制字的累加功能,从而得到ROM的寻址地址;正弦波ROM的数字位宽为8位,存储深度为256;相位控制器设置模块主要完成设置三个正弦波a、b、c的初相位差为120o的功能。由于正弦波ROM的地址线宽度为8位,而地址累加器地址宽度为16位,所以本文取地址累加器的高8位与正弦波ROM的地址线相连接。

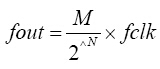

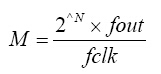

本文设置正弦波a、b、c的输出频率fout为工频信号频率50Hz,令时钟信号fclk为10kHz,频率控制字M由以下公式计算。

(1)

(1)

公式转换得:

(2)

(2)

此将数据代入公式(2),可计算出频率控制字M等于327.68,取整数等于328。

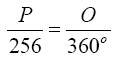

三路正弦波的初始相位设置由相位控制字设置模块完成,该模块主要完成将地址累加器的输出地址分别加上三个相位控制字再输出到正弦ROM。设相位控制字为P,对应初相为O,则计算公式如下:

(3)

(3)

因此,根据已知三相正弦波初相O分别为0o、120o、240o,代入公式(3),可求得对应的相位控制字取整数后分别为0、85、171。

3 三角波发生器模块

三角波发生器模块的设计通常有两种方法完成:(1)采用计数器方法,利用VHDL语言设计一个向上向下计数器,从0开始计数,当计数到256后再向下计数,当计数为0时,再重复以上过程。将计数器的数据输出就得到三角波数据输出,这种方法得到的三角波频率由计数器时钟决定。(2)采用DDS原理方法,具体的实现与正弦波发生器实现的原理一样,区别在于将正弦波原理框图中ROM的正弦波数据换成三角波数据。三角波频率的选择可以根据实际电路设计需要来确定,本设计中设置了三角波输出频率为3KHz,三角波频率越大,对正弦波的采样率越高,使输出的SPWM波形经过LC滤波还原为正弦波时谐波越小。

4 数据比较器模块

数据比较器模块主要完成将正弦波

VHDL SPWM DDS 死区时间 FPGA 201505 相关文章:

- 基于FPGA的三相PWM发生器(06-23)

- 基于CPLD的高速可程控数字延迟线系统的设计(08-02)

- 基于CPLD在臭氧电源中的应用(08-19)

- 基于SPCE061A和CPLD的电动自行车充电系统研制(10-22)

- 基于FPGA电火花加工脉冲电源的设计与研究(11-11)

- 一种高效多串口单一中断源的芯片设计(11-14)