分析便携式设备中的电源效率

上述电压参考在低频率下支持90dB。输出电压变化的标准偏差是 0.5%,在–40℃至125℃温度范围内的温度系数为15ppm/℃。这些特性可在1.6V至5.5V的电源电压范围内实现。可实施各种用于为电压参考实现输入噪声抗扰度的方法。

介绍

几乎每款模拟电路都需要高精度高稳定参考电压或电流源。不过,在选择片上系统(SoC) 技术时,参考电压模块不应成为限制因素。也就是说这类系统所选用的技术工艺对于参考电压源来说并不一定总是最理想的。因此,其设计应该更稳健,才能适应各种技术工艺的变化。

电池通常可作为SoC的电源。这就更需要提高工作在大电源电压范围内的电压参考源的线性稳压性能。要延长电池使用寿命,就需要低静态电源电流。同时,还需要在宽泛频率下实现高电源抑制比(PSRR),以抑制来自高速数字电路、降压转换器或片上其它开关电路的噪声。本文主要介绍具有高PSRR的超低静态电流带隙电压参考。

基本带隙电压参考结构

改善 PSRR的主题思想是在低压降稳压器(LDO)后面布置一个带隙电压源。现有线性稳压器拓扑在静态电流、DC负载稳压、瞬态响应、去耦电容以及硅芯片面积要求方面存在很大差异。由于我们的目标是在没有外部电容器的情况下,在同一芯片上提供全面集成型LDO,因而典型LDO结构并不适合。

这些结构与超低静态电源电流相矛盾。为了缓解这一矛盾,您可为LDO 使用与参考源相同的带隙。不宜采用标准LDO结构的原因在于它需要输出电容器来实现稳定工作。最佳选项是带一个增益级的结构,其无需输出电容器便可实现稳定。

低压降稳压器

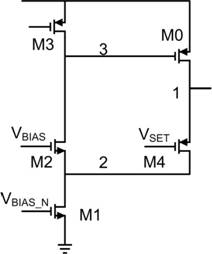

图1是该设计[1]中所使用LDO的内核及其简化原理图。图1[2]中的M0和M4代表翻转电压跟随器(FVF),其可实施无逆向功能及相关极点的单级稳压。静态电流由晶体管M1和M3确定。晶体管M2 可作为共栅放大器。

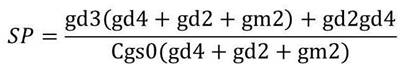

LDO的开环增益由第一个级联级(即晶体管M2和M3)决定。可作为负载的 M4 PMOS跟随器存在低阻抗源,因此 FET M0的输出增益接近1。在图2中的小型信号等效电路的帮助下,对所推荐的 LDO结构进行稳定性分析,结果显示只有一个极点(公式1):

可作为补偿电容器的M0栅源电容器可创建 LDO的主极点。因此无需去耦片外电容器,便可使LDO[3]稳定。

图1.具有翻转电压跟随器、无输出电容器的LDO

图2.LDO的小型信号等效电路

这种LDO的另一项优势是简单的自启动程序,其无需专用电路。最初,在电压VDD 为 0 时,VOUT也为 0,跟随器M4 在无反馈的情况下关闭,M1的偏置电流大于M3的偏置电流。因此,栅极电压M0 不仅可降低,而且还可驱动输出电压VOUT至所选的输出电压值。

这种架构的缺点是线路稳压及 PSRR差。原因在于低开环增益,因为它仅由一个增益级决定。合理的解决方案可能是第一级的级联电流源,其可提高增益,进而可提高线路稳压性能和PSRR。

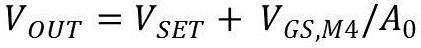

图1中的LDO输出电压为(公式2):

其中,VSET为参考电压,VGS,M4是M4的栅源电压。

因此,输出电压对温度和工艺变化极为敏感。要避免这种问题,就必须创建一个更为理想的跟随器,其中 M4 是反馈环路的一部分(图3)。

图3.M4位于放大器反馈环路中、无输出电容器的LDO。

这种情况下的输出电压为公式3:

其中,A0是放大器的开环增益反馈。对于高反馈放大器增益而言,可使用公式4:

图4.具有电阻式分压器、M4位于放大器反馈环路、无输出电容器的LDO

在反馈环路(图4)中添加电阻式分压器后,输出电压转变为:

VOUT=VSET(1+R1/R2)

FVF反馈放大器不影响整体 LDO稳定性,因为它位于主LDO反馈环路的外部。对于本地反馈环路而言,只要求设计方案稳定。

带隙内核说明

所选用的带隙内核(图5)采用在标准CMOS 技术中广泛使用的经典结构。

图5.所推荐带隙电压参考内核的简化方框图

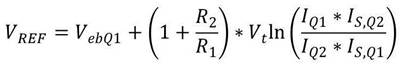

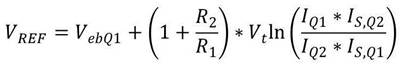

通过添加双极性晶体管的负温度系数基射极间电压,可获得带隙电压的低温系数,从而可通过在不同电流密度下偏置的两个基射极间电压之差获得正温度系数电压。为电阻器R2和R3选择相等的值,参考电压就可表示为公式5:

其中VEB是Q1的基射极间电压,VT是热电压,IQ1和IQ2是通过晶体管Q1和Q2的电流,而 IS,Q1和IS,Q2则分别是Q1和Q2的饱和电流。

误差源

要为任何带隙电压参考实现良好的精确度,必须定义总体精度误差的主要形成因素[4]。以下是所推荐架构

功耗嵌入式电 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)