基于FPGA的数字锁相环平台的搭建

时间:12-05

来源:互联网

点击:

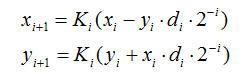

表示为:

其中:

以上方程在硬件中实现非常简单,因为乘 操作可以通过右移来实现。

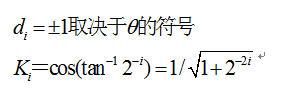

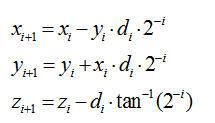

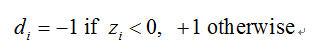

把增益因子![]() 从迭代方程中移除,基于移位-相加的CORDIC算法方程如下:

从迭代方程中移除,基于移位-相加的CORDIC算法方程如下:

其中:

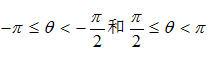

以上方程在

范围内的任意角度都能收敛。如果要在整个直角坐标系上工作,还必须把

映射到

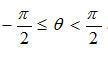

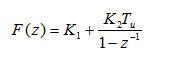

。此外,还必须补偿增益因子,定义![]() 为:

为:

其中n是CORDIC算法的迭代计算次数。![]() 的值取决于迭代次数n,在n确定的情况可以视为一个常数。当n趋于无穷大时,

的值取决于迭代次数n,在n确定的情况可以视为一个常数。当n趋于无穷大时,![]() 的值为0.60725。因为

的值为0.60725。因为![]() 和

和 是常数,可以预先存在一个很小的查找表里。

是常数,可以预先存在一个很小的查找表里。

3、环路设计及分析

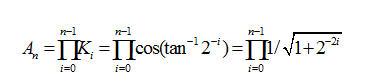

基于跟踪性能和稳定性的折中考虑,接收机一般采用二阶环。在本设计中,我们采用了理想型积分环路滤波器。理想型积分环路滤波器的锁相环有更佳的跟踪性能,在固定频偏下,无稳态相位误差。

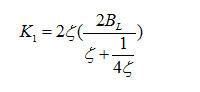

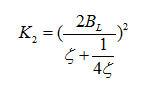

一阶理想型积分环路滤波器的数字域表达式:

四、设计仿真

用MATLAB软件搭建锁相环的核心仿真平台,包括中频欠采样,数字前端分成I、Q两路信号,AGC,CORDIC混频,积分抖落滤波器,修正的正切相位提取器,环路滤波器,NCO,锁定检测等。

(1)、系统框图

(2)、仿真结果

1、AGC的仿真,输入AGC的I、Q两路信号幅度为0.01V Vpp,从仿真图中可用看出AGC输出的幅度为1V Vpp,锁定时间在3ms左右。

2、相位误差以及多普勒频偏的估计的仿真,在仿真中我们设定的多普勒频偏为1kHz,从下图的仿真结果锁定后的相位误差非常小,所得到的多普勒频偏的估计也恰好为1KHz。

FPGA数字锁相 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)