基于Virtex-6 FPGA的三种串行通信协议测试及对比(一)

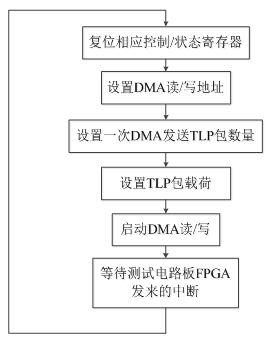

PCIe接口对测试板FPGA控制/状态寄存器进行读/写操作,来控制DMA的进程。每次DMA完成后,处理板FPGA会向服务器CPU发送一次中断。服务器对测试电路板FPGA DMA传输的控制流程如图6所示。

图6 PCIe 2.0 DMA传输控制流程图

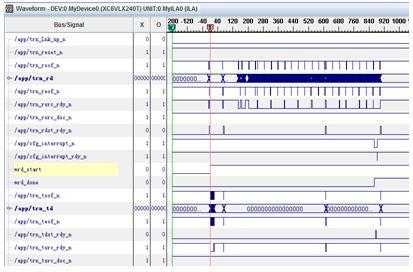

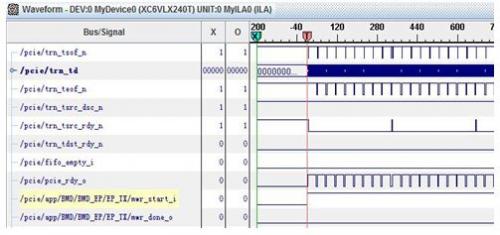

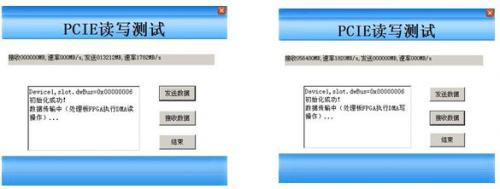

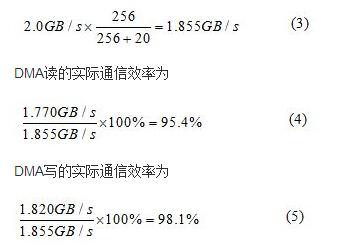

本测试将TLP包载荷数设为256Bytes(IP核允许的最大值),每次DMA传输的TLP包的数量为16384,故每次DMA传输的数据量为4MB.使用ChipScope软件观察FPGA内部的PCIe 2.0 DMA读/写相关信号,如图7,图8所示。本测试开发了PCIe读写功能测试软件,实现PCIe传输数据量和传输速率的实时显示。传输速率通过1s内DMA传输完成的次数来计算。测试结果如图9(a)、(b)所示。PCIe 2.0 DMA读的数据传输速率为1.770GB/s,DMA写的数据传输速率为1.820GB/s.

图7 PCIe 2.0 DMA读测试信号波形

图8 PCIe 2.0 DMA写测试信号波形

图9 PCIe 2.0 DMA读写速率测试结果(a)DMA读测试(b)DMA写测试

下面分析并计算本测试条件下PCIe 2.0 DMA读/写的理论传输速率和实际通信效率。

PCIe 2.0协议主要开销为8B/10B编码开销和数据包传送开销。PCIe总线以包的形式在不同器件之间交换信息。数据在进入处理层后会被封装一个包头,该包头长度在32bit地址下为12字节(本测试采用32bit地址)。当数据包进入数据链路层后,会添加2字节的序列号和4字节的LCRC字段。数据包进入物理层后,使用1字节的开始字符和1字节的结束字符将其封装成帧。

在DMA写测试中,FPGA每发送一次存储器写报文(含256字节数据)会带来20字节的额外开销。在DMA读测试中,FPGA向服务器发送存储器读报文,并由服务器返回完成报文(含256字节数据)。每返回一次完成报文会带来20字节的额外开销。由于PCIe 2.0定义了流量控制缓存管理机制,允许服务器返回完成报文的同时接收FPGA发来的存储器读报文,故DMA读测试中可忽略FPGA发送存储器读报文带来的开销。

故PCIe 2.0 DMA读/写的理论速率相同,均为

5 Serial RapidIO 2.0通信测试

RapidIO是针对嵌入式系统芯片间和板间互连而设计的一种开放式的基于包交换的高速串行标准,已在电信、国防等行业大量使用。

Serial RapidIO(简称SRIO)是物理层采用串行差分模拟信号传输的RapidIO标准。SRIO 2.0协议性能进一步增强,链路线速率可达6.25Gb/s,在电气层支持热插拔,并新添了控制符号和空闲模式功能。

本测试以测试电路板FPGA作为发起端,以测试电路板DSP作为目标端。通过FPGA向DSP发送SWRITE包,进行SRIO 2.0写测试,通过FPGA向DSP发送NREAD包,DSP向FPGA返回RESPONSE包,进行SRIO 2.0读测试。

Virtex-6FPGA通信协 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)