基于Virtex-6 FPGA的三种串行通信协议测试及对比(一)

在高性能雷达信号处理机研制中,高速串行总线正逐步取代并行总线。业界广泛使用的Xilinx公司Virtex-6系列FPGA支持多种高速串行通信协议,本文针对其中较为常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三种协议进行了测试及对比分析。首先搭建了基于Virtex-6 FPGA的高速串行协议测试平台;然后设计并分别实现了三种协议的高速数据通信,测算了协议的实际传输速率;最后结合测试结果,从协议层次结构、链路数目、链路线速率、数据传输方式、协议开销、拓扑结构、设备寻址方式、应用领域等方面对三种协议进行了比较。本文研究工作可为三种协议的选用、测试和工程实现提供参考。

1引言

随着雷达带宽和AD采样率的提高,在高性能雷达信号处理机研制中,系统对数据传输带宽的要求不断增加,高速串行总线正逐步取代传统的并行总线。

Xilinx公司推出的Virtex-6系列FPGA,在片上集成了固化的GTX模块,以提供高速串行通信支持。同时Xilinx公司提供有多种串行通信协议IP核,便于用户进行开发。Aurora 8B/10B,PCI Express 2.0和Serial RapidIO 2.0是其中较为常用的三种协议。目前已有众多文献涉及到三种协议基于FPGA的实现方案。然而这些方案未能充分发挥协议性能,存在线速率较低(仅为2.5Gb/s)或未实现多通道绑定。针对上述问题,本文基于Virtex-6 FPGA,分别实现了三种协议在4x链路,5.0Gb/s线速率模式下的数据通信,测得协议的实际传输速率,并对三种协议的特点与应用进行了对比分析。

2测试平台简介

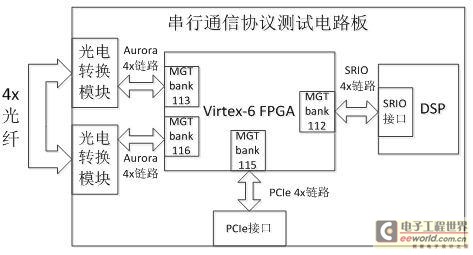

本文以实验室自行开发设计的PCIe光纤接收处理板(以下简称测试电路板)为测试平台。测试电路板的结构图和实物图分别如图1,图2所示。其中,FPGA选用XC6VLX240T-2FF1156,该芯片含20个GTX收发器,链路线速率可达6.6Gb/s.DSP选用TMS320C6678,该芯片含有SRIO接口,支持1x、2x和4x链路。光电转换模块选用FCBG410QB1C10,它包含4条链路,带宽可达40Gb/s.故而测试电路板的硬件设计符合本测试对数据传输速率的要求。

图1测试电路板模块结构和链路连接图

图2测试电路板实物图

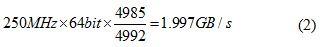

如图3所示,将测试电路板插入服务器主板的PCIe插槽中,并将光纤接入测试电路板,完成测试平台的搭建。本测试中,PCI Express 2.0协议用于实现FPGA与服务器的数据通信,Serial RapidIO 2.0协议用于实现FPGA与DSP的数据通信,Aurora 8B/10B协议用于实现FPGA的光纤自发自收通信。由于三种协议都在物理层进行8B/10B编码,故在本测试工作模式下,它们的极限速率均为

图3测试平台搭建

3 AURORA 8B/10B通信测试

Aurora 8B/10B协议是Xilinx公司针对高速传输开发的一种可裁剪的轻量级链路层协议,通过一条或多条串行链路实现两设备间的数据传输。协议Aurora协议可以支持流和帧两种数据传输模式,以及全双工、单工等数据通信方式。

本测试中,Aurora 8B/10B IP核配置为双工、流模式,参考时钟频率250MHz.

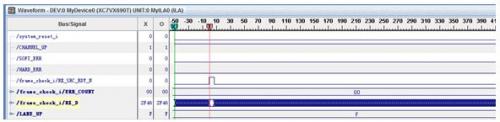

使用ChipScope软件观察FPGA相关信号如图4所示。观察RX_SRC_RDY_N可以发现,平均每4992周期出现7个周期的数据无效信号。由于接收数据时钟频率为250MHz,数据位宽为64bit,故本测试中,Aurora 8B/10B协议单向传输速率为,

图4 Aurora 8B/10B协议通信测试信号波形

下面分析协议理论传输速率和实际通信效率。该协议的帧格式比较简单,除2字节的起始标志,2字节终止标志和至多1字节的填装字符外,其余为数据部分。本测试采用的流模式是以无结尾的帧方式实现。故协议除8B/10B编码外,基本上不存在其他开销。故根据(1)式可得,协议的理论速率为2.0GB/s,协议的实际通信效率为99.75%.

4 PCI Express 2.0通信测试

PCI Express(简称PCIe)总线技术是取代PCI的第三代I/O技术。PCIe采用串行点对点互连,允许每个设备拥有专属的一条连接,不争夺带宽资源,同时保证了数据的完整性。PCI Express 2.0协议的链路线速率达到5Gb/s,最高支持32x链路。

本测试中,PCIe 2.0通信测试通过FPGA对服务器内存的DMA读/写操作来实现。

服务器方面,本测试选用Windriver软件进行PCIe驱动程序的开发。利用该软件提供的PCIe驱动程序及用户接口函数,编写符合本测试功能需求的程序。

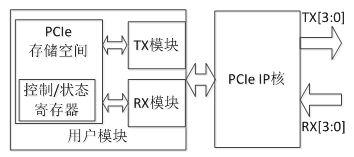

FPGA方面,本测试通过设计用户模块,实现对PCIe IP核的控制,完成DMA读/写操作。FPGA模块结构如图5所示。

图5 PCIe 2.0通信测试FPGA模块结构 为便于服务器对测试电路板FPGA进行控制,在FPGA的PCIe存储空间模块中,定义了若干控制/状态寄存器,这些寄存器的作用有:DMA读/写初始化,控制DMA读/写的启动与停止,标志一次DMA传输是否完成,设置一次DMA传输的数据量等。

服务器通过

Virtex-6FPGA通信协 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)