为ASIC和SoC选择最优嵌入式存储器IP

构,因此,它既无需修改掩膜,也无需额外的流程步骤。此类IP宏块具有更高的成本效益(流程成本可节省15-20%),并且可在任何工厂进行加工,也可出于成本或生产能力等原因,改换加工工厂。这种解决方案提供了多种尺寸、长宽比和接口,可逐一指定相应的存储器编译器。对于系统的其余部分来说,生成的存储器块接口看起来就像静态RAM,但其密度(位/单元空间)是基于6T存储单元的存储器阵列的2倍(经过对作为空间计算一部分的全部支持电路的平均)。对于大型存储器阵列来说,支持电路所需全部空间所占百分比较小,存储器块的空间利用率也更高。

存储器编译器工具

嵌入式存储器编译器的职责是,针对特定存储器应用程序的确切需求,量身定做基本的IP存储器宏单元。若适用范围足够广,编译器可允许设计师选择最优架构,自动生成存储器阵列,并精确确定优化程序所需的速度、密度、功率、成本、可靠性以及大小等因素。通过编译器的自动化操作,可降低非经常性工程成本,并可减少手动阵列优化相关的潜在错误。编译器不但可使客户的内核大小、接口以及长宽比均达到最理想数值,而且还可帮助他们最大限度地缩短上市时间。作为编译流程的一部分,编译器还可向设计师提供存储器阵列的电气、物理、仿真(Verilog)、BIST/DFT模型以及综合视图。

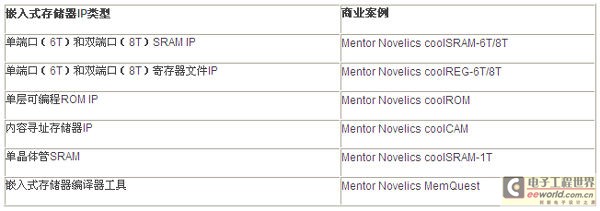

表2:嵌入式存储器IP的商业案例

结论

为ASIC/SOC选择最优嵌入式存储器IP是设计决策的关键。设计师应了解适用于其特定应用程序的最佳存储器特性的所有关键参数,其寻求的存储器IP应具有足够的适应性,可满足目标SoC的各种需求。尽管有现成的免费存储器IP可供使用,但与可为特定应用程序提供更好特性的收费IP相比,它并不能总是提供最佳解决方案。

经过充分调试的存储器IP具有体积小、泄露功率低、动态能耗低、速度快等特点,可使设计师的解决方案进一步优化,不但可在产品的整个寿命周期内,带来上百万美元的结余,而且也使其芯片在竞争激烈的ASIC/SOC市场上,得到更好的差异化。

ASICSo 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)