电子产品设计初期的EMC设计考虑

随着产品复杂性和密集度的提高以及设计周期的不断缩短,在设计周期的后期解决电磁兼容性(EMC)问题变得越来越不切合实际。在较高的频率下,你通常用来计算EMC的经验法则不再适用,而且你还可能容易误用这些经验法则。结果,70% ~ 90%的新设计都没有通过第一次EMC测试,从而使后期重设计成本很高,如果制造商延误产品发货日期,损失的销售费用就更大。为了以低得多的成本确定并解决问题,设计师应该考虑在设计过程中及早采用协作式的、基于概念分析的EMC仿真。

较高的时钟速率会加大满足电磁兼容性需求的难度。在千兆赫兹领域,机壳谐振次数增加会增强电磁辐射,使得孔径和缝隙都成了问题;专用集成电路(ASIC)散热片也会加大电磁辐射。此外,管理机构正在制定规章来保证越来越高的频率下的顺应性。再则,当工程师打算把辐射器设计到系统中时,对集成无线功能(如Wi-Fi、蓝牙、WiMax、UWB)这一趋势提出了进一步的挑战。

传统的电磁兼容设计方法

正常情况下,电气硬件设计人员和机械设计人员在考虑电磁兼容问题时各自为政,彼此之间根本不沟通或很少沟通。他们在设计期间经常使用经验法则,希望这些法则足以满足其设计的器件要求。在设计达到较高频率从而在测试中导致失败时,这些电磁兼容设计规则有不少变得陈旧过时。

在设计阶段之后,设计师制造原型并对其进行电磁兼容性测试。当设计中考虑电磁兼容性太晚时,这一过程往往会出现种种EMC问题。对设计进行昂贵的修复通常是唯一可行的选择。当设计从系统概念设计转入具体设计再到验证阶段时,设计修改常常会增加一个数量级以上。所以,对设计作出一次修改,在概念设计阶段只耗费100美元,到了测试阶段可能要耗费几十万美元以上,更不用提对面市时间的负面影响了。

电磁兼容仿真的挑战

为了在实验室中一次通过电磁兼容性测试并保证在预算内按时交货,把电磁兼容设计作为产品生产周期不可分割的一部分是非常必要的。设计师可借助麦克斯韦(Maxwell)方程的3D解法就能达到这一目的。麦克斯韦方程是对电磁相互作用的简明数学表达。但是,电磁兼容仿真是计算电磁学的其它领域中并不常见的难题。

典型的EMC问题与机壳有关,而机壳对EMC影响要比对EMC性能十分重要的插槽、孔和缆线等要大。精确建模要求模型包含大大小小的细节。这一要求导致很大的纵横比(最大特征尺寸与最小特征尺寸之比),从而又要求用精细栅格来解析最精细的细节。压缩模型技术可使您在仿真中包含大大小小的结构,而无需过多的仿真次数。

另一个难题是你必须在一个很宽的频率范围内完成EMC的特性化。在每一采样频率下计算电磁场所需的时间可能是令人望而却步的。诸如传输线方法(TLM)等的时域方法可在时域内采用宽带激励来计算电磁场,从而能在一个仿真过程中得出整个频段的数据。空间被划分为在正交传输线交点处建模的单元。电压脉冲是在每一单元被发射和散射。你可以每隔一定的时间,根据传输线上的电压和电流计算出电场和磁场。

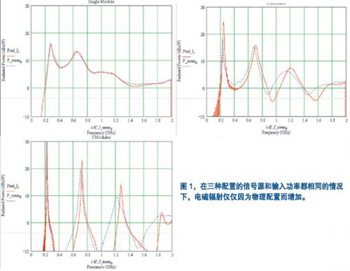

EMC仿真可得出精确的结果。图1对装在一块底板上的三种模块配置(即1块、2块和3块模块)的辐射功率计算值(红色)与辐射功率实测结果(蓝色)进行了比较,(参考文献1)。辐射功率计算值以1nw 为基准,单位为dB 。你可以把多个模块配置的谐振峰值位置存在的小差异归因于在测量中难以将多个模块精确对准。值得注意的是,由于三种配置的输入功率都相同,所以辐射功率的谐振峰值和幅度的差异仅仅是由于系统布局不同引起的。

对装在一块底板上的三种模块配置

潜在应用领域

EMC仿真可用于检测元件和子系统,如散热器接地的辐射分布对频率特性影响,也可用于评价接地技术、散热器形状的影响及其它因数。此外,你还可比较不同通风口尺寸与形状以及金属厚度的屏蔽效果。在该领域的最新应用中,有一项研究工作是对采用大口径通风口进行送风并通过放置两块背靠背间隔很小的板来达到屏蔽效果这种方法进行评估。

EMC仿真也适用于系统级电磁兼容设计和优化,以便计算宽带屏蔽效果、宽带电磁辐射、3-D远场辐射图、用来模拟转台式测量情况的柱形近场电磁辐射以及用以实现可视化,有助于确定电磁兼容热点位置的电流和电磁场分布。典型的系统级EMC应用有:确保最大屏蔽效果的机壳设计,机壳内元件分布位置的EMC 效果评估,系统内外缆线耦合的计算以及缆线辐射效果的检测。EMC仿真还有助于发现有害电磁波在机壳和子系统中的机理,如空腔谐振,穿过孔、插槽、接缝和其他机座开口处的电磁辐射,通过缆线的传导辐射,与散热器、其他元件的耦合,以及光学元件、显示器、 LED和其他安装在机座上的元件固有的寄生波导。

接头类型对EMC 的影响

你可以使用简单而快速建立的机壳模型来进行接缝配置方面的设计折衷。图2对对接接头产生的辐射与重叠机壳接缝产生的辐射作出评估。通过比较相对的屏蔽水平,工程师就可以根据机壳的EMC预算和实现特定设计配置的成本来做出决定。仿真过程中增加内部元件仅仅对仿真时间产生很小的影响,所以设计师可以方便地在引起插槽谐振间耦合、谐振腔模式以及与内部结构的交互作用的真实环境下对接缝屏蔽效果进行评估。插槽泄漏的设计规则不适用于以上几个因素,会导致成本高昂的过设计和欠设计。

EMC设计 相关文章:

- 基于仿真软件的系统EMC设计之工程实例(01-12)

- 电磁兼容EMC设计及测试技巧(01-19)

- 电子线路中的EMC标准与EMC设计(02-03)

- 舰载天线稳定平台EMC设计(09-06)

- EMC设计时应该注意的问题(09-06)

- 混合集成电路EMC的设计(10-06)