LD0与VLD0的设计原理及性能测试

时间:05-09

来源:电源技术应用

点击:

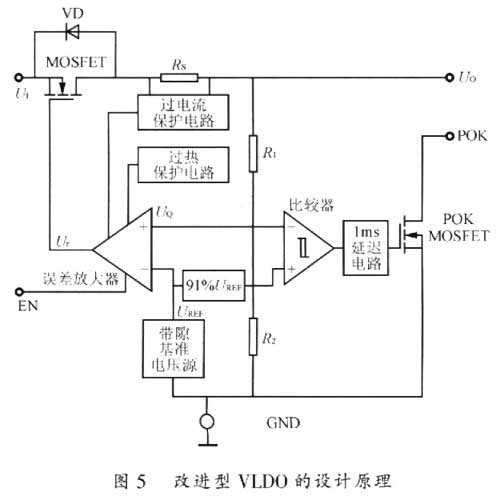

平,令POK MOSFET截止,POK端输出为高电平,以此表示电源正常。POK MOSFET采用开漏极输出结构,外部需经过lO kΩ~l MΩ的上拉电阻接U0端。不用POK端时可接地或悬空。EN为使能控制端,当EN端接低电半时将电源关断。LDO进入休眠状态,此时POK端呈高阻态。利用延迟电路能避免因干扰而造成的误动作。

3 几种线性稳压器的性能比较

几种线性稳压器的性能比较见表l。

4 LDO的性能测试

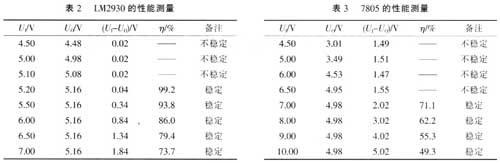

为了说明低压差稳压器的优良特性,现将LM2930与普通三端稳压器7805作一对比性试验,二者的标称稳压值均为5v。稳压器的输入电压取自HT-1714C型多路直流稳压电源。稳压器的输出端接上假负载R1,使输出电流I0=100mA。输出电压U0用DT860型数字万用表测量。测量数据以及汁算出的压差值(U1-U0)、稳压电源的效率(η)一并列入表2及表3中。由表2及表3可见,当U1>5.20V时,LM2930即可正常稳压,稳压值U0=5.16v;当u1=5.20V时的压差仅为0.04 V,U1=5.50V时为0.34V,均低于O 6V。7805则不然,其压差必须大于2V(实际使用时应在4V以上),才能正常稳压,稳压值U0=4.98V。

5 结语

不难看出,选择低压差稳压器能显著提高线性集成稳压电源的效率。

- 便携式医疗设计中的无线发展趋势(05-09)

- 便携式仪器在射频测试中扮演的角色(09-02)

- 将iPhone5、iPad变身为便携式示波器(08-07)

- 可随时随地无线充电 TDK电磁诱导式充电技术(09-29)

- 基于Qt实现USB CDC便携式设备串口通信客户端设计(05-14)

- 模块化在便携式设备设计中的应用(10-07)