基于DDS技术的动态偏振控制器驱动电路研究

时间:08-03

来源:互联网

点击:

式中:fo是输出频率;fref为DDS参考时钟频率,由FPGA将晶振输入时钟经内部锁相环分频后产生。

由相位步进累加可得到相位码,再寻址波形存储器即可完成相位――幅度转换,得到相应的幅度码,输出给主模块。由于驱动信号为正弦波,波形存储器直接调用FPGA内部模块sin_COS_lookup_table,输入与输出数据位宽均为16位。DDS子模块流程图如图6(b)所示。

2.4 实验测试结果

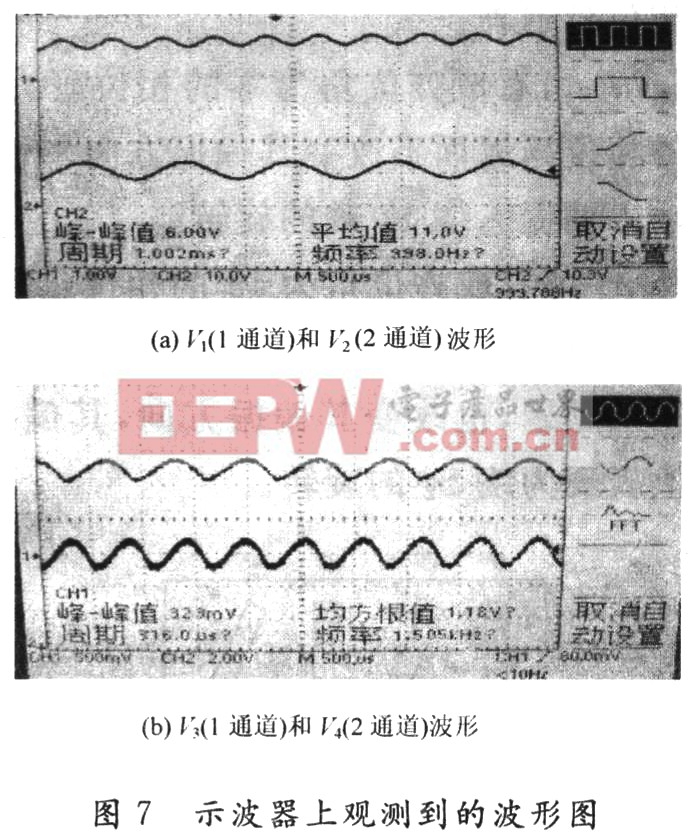

实验时设定4路正弦驱动信号V1,V2,V3,V4的频率分别为f1=2 000 Hz,f2=1 000 Hz,f3=1 800 Hz,f4=1 500 Hz。

示波器上观测的波形如图7所示。

波形使用双通道示波器观测,2通道探头设置为10档。从图7中可以看出,输出波形较为稳定。如果在FPGA程序内增大sin_COS_lookup_table模块的输入数据位宽,也即增大采样点数,可以得到精度更高的输出波形。

3 结 语

动态偏振控制器目前广泛应用于光纤通信和传感领域,是一种重要的偏振控制器件。分析动态偏振控制器的工作原理,并以光纤挤压型偏振控制器为研究对象,设计了基于DDS技术和FPGA的调制电路,该设计以偏振度测试系统为实验平台。实验测试结果表明,所设计的调制电路能够输出4路频率可调的正弦信号,输出信号稳定,控制灵活,工作性能可靠。该方法思路简单,采用Verilog语言设计并调用FPGA内部模块,设计灵活透明,且外围电路较为简易,具有良好的实用性和性价比。

驱动 电路 研究 控制器 动态 DDS 技术 基于 FPGA 相关文章:

- 基于低压驱动RFMEMS开关的MEMS开关改进(11-09)

- 采用射频功率放大器驱动器的无线系统设计(04-10)

- 低压驱动的RF MEMS开关模拟设计(10-10)

- 多串流MIMO驱动 11ac射频前端迈向28nm(08-20)

- PCB设计后期检查的几大要素(04-20)

- 工业伺服驱动器的保护设计方案(06-21)