基于低噪音单芯片高频分频器的PLL设计

VSAT是一种小卫星通信系统,可为边远地区的家庭和商业用户提供可靠的、具有成本效应的宽带数据和其它业务。VSAT采用一种小型天线来发送和接收卫星信号,可为所有处于卫星覆盖区域内的用户提供高带宽连接,无论用户地点附近是否有通信基础设施。

目前全球使用的VSAT超过100万只,同时预计还有大量的潜在用户。美国约有3,000万人居住在相对边远的地区,他们都是VSAT的潜在用户。在英国,由于电缆敷设率相对较低,而电话交换设备距离较远限制了ADSL(非对称数字用户线)的普及,30%以上的人口都有望发展为VSAT用户。

为了加强乡村地区的宽带接入服务,英国政府目前正在加快处理VSAT上行链路频道的授权。与此类似,欧洲也精简了授权机构的规章程序,以便顺利布署VSAT。与此同时,VSAT市场的不断发展使设备供应商所面临的压力越来越大,他们必须减少VSAT系统的成本并简化其使用。

图1是从欧洲频谱分配信息网摘取的一个例子,从中我们可看出在3 GHz-15GHz频谱范围内的无线应用。欧洲电信标准协会已将高频的Ku频段分配给VSAT上行链路。上行链路工作于14-14.5GHz之间,下行链路则工作于12.5-12.75GHz或10.7-11.7GHz之间。其它国家的频段分配情况大致相同。

基于低噪音单芯片高频分频器的PLL设计

为了在这些频段内正常工作,VSAT设计者需要一个稳定的低噪音高频信号源。VSAT中的中频(IF)频段通常为950-1,450MHz,需要一个工作频率为13.05GHz的本地振荡器。迄今为止,设计者仍然只能通过频率倍乘来产生工作于这一频段的IF源。

图2所示为一个标准的频率乘法器。它的原理是:将一个稳定的频率源送入非线性的电路中,然后选择性地产生想要的谐波输出。这一输出经过严格的滤波,然后通过线性放大器重新放大,进行损失补偿。

由于谐波级数越高其输出越低,为了将频率从一个低阶的参考源(如晶振)升高到微波频率,我们需要多级电路。这就是频率乘法器的缺点,它常常使设计变得非常复杂而且昂贵,且效率却很低。另一方面,乘法器也有其优点,那便是它几乎可以达到任何想要的高频。

低成本的高频PLL

新一代的低噪音高频单芯片分频器为RF设计者提供了一种低成本的高性能解决方案,可用来取代频率乘法器。采用Zarlink提供的13.5GHz分频器,设计者可通过成本较低的锁相环(PLL)电路为VSAT和其它RF器件构建高频源。分频器可扩展单芯片频率合成器的输出范围,从而保证工作于高频的 PLL的相关正向设计得以顺利进行。

图3是一个基频合成器电路,它由一个压控振荡器(VCO)、一个可变分频器和一个相位比较器构成。

基于低噪音单芯片高频分频器的PLL设计

加在VCO上的控制电压决定了VCO的输出频率。相位比较器产生的电压与两个输入信号的相位差成比例。这一电压控制着VCO的频率,从而保证通过分频器后(fN)从VCO反馈回来的相位比较器输入频率与参考输入fr的相位一致,以此保证频率相同。因此,VCO的频率保持为N×fr。这样的合成器将生成一系列间隔为fr的频率。

单芯片频率合成器的最大范围通常限制在2-3GHz,一方面是受市场决定,另一方面则因为频率太高时合成器的功耗会过大。为了产生高频源,合成器通常在PLL中与一个独立的外部分频器进行耦合。这个分频器将频率源“预分”到一个可被合成器处理的频率。

PLL价廉物美,但目前为止,它们的最大频率受低噪音商用分频器的频率响应限制。

13.5GHz分频器上市后,设计者可使用低成本的标准元件来构建PLL,从而提供VSAT和其它RF器件所需的高频率。

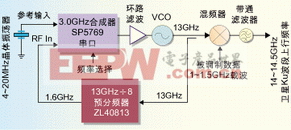

图4说明了如何使用PLL电路来创建VSAT上行链路本地振荡器。该设计需要一个噪音性能较好的单芯片频率合成器,如SP5769。这种芯片的最大工作频率为3GHz,但通过ZL40813 13.5GHz器件将VCO的输出除以8后(为1.6GHz),可将频率扩展到13.5GHz。1.6GHz输入在SP5769中被进一步分频,然后与晶振参考频率相比较。SP5769的输出通过一个充电泵,控制VCO的输入,构成一个闭合回路。

基于低噪音单芯片高频分频器的PLL设计

该电路也可以使用其它单芯片频率合成器,不过应注意选择那些能与高频预分频器接口的合成器。

在基于BiCMOS技术的合成器中,有些电路的工作速度可能相对较低,因此不能很好地配合高频分频器。

诚然,低相位噪音对VSAT和其它RF器件都十分重要。本例电路中的13.5GHz分频器是采用互补硅双极技术构建的,Ft为28GHz。这样在回路带宽中产生的噪音与载波的噪音十分接近,不会被PLL消除。

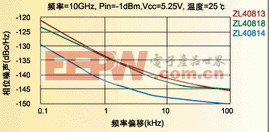

噪音级数与材料的物理特性有关,如GaAs等其它技术本身的噪音级数就比载波噪音要高。图5列举了其它13.5GHz分频器的相位噪音级数。

基于

- 锁相环中的DLL和PLL的区别(07-25)

- 基于X波段的经典设计汇总,包括天线、振荡器、滤波器等(12-29)

- 多路SDI信号单波长无损光传输(02-11)

- 一种基于PLL的P波段可控频率源(04-01)

- 基于DDS+PLL的跳频信号源的设计(06-25)

- AD9779A的寄存器配置及PLL频带优化(03-11)