基于ADF4360-1的本振源设计

0 引 言

在无线通信领域,本振信号性能的优劣是影响混频器输出频谱纯度的主要因素。频率合成技术是指由一个稳定、准确的标准参考频率,经过一系列的处理过程,产生大量离散的具有同一稳定度和准确度的信号频率。锁相式频率合成器是一种建立在相位负反馈基础上的闭环控制系统,主要由鉴相器、环路滤波器和压控振荡器组成。

通过锁相频率合成实现的频率源在通信、CATV等领域得到了广泛应用,很多现代电子设备和系统的功能实现都直接依赖于频率源的性能。ADI公司生产的ADF4360-1是电流型电荷泵数字锁相式频率综合器芯片,具有很高的性价比。

1 ADF4360-1的工作原理及主要性能

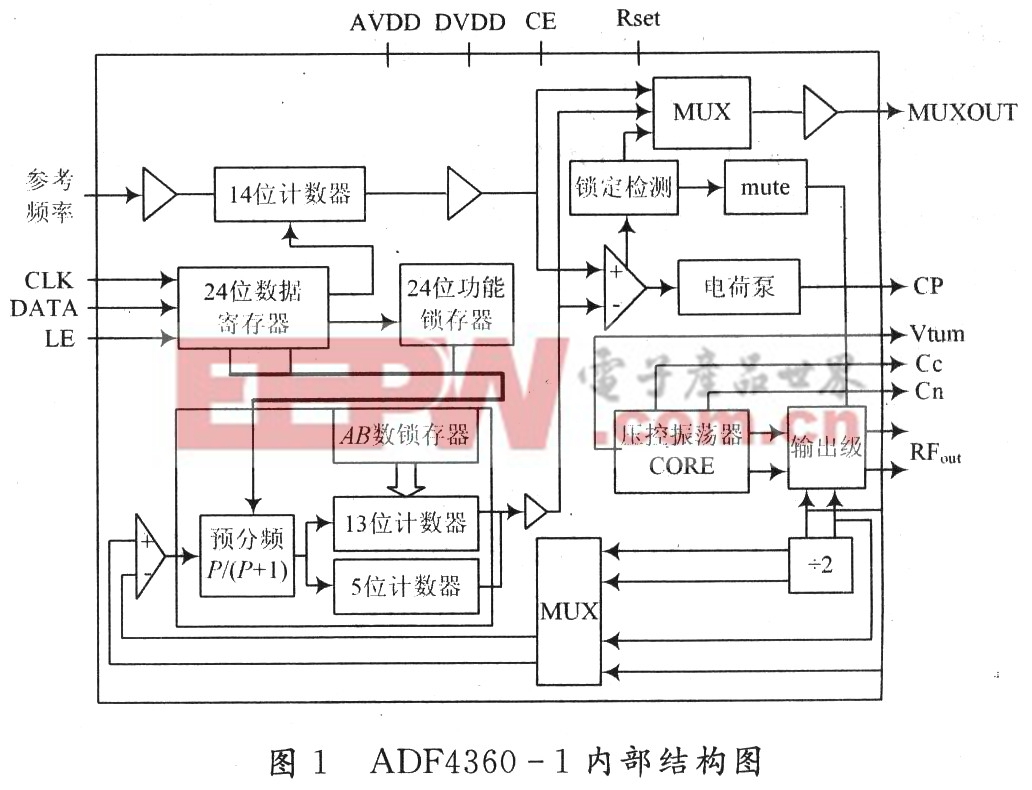

ADF4360-1主要由数字鉴相器、电荷泵、分频器、计数器及双模前置P/(P+1)分频器等组成。如图1所示。

1.1 工作原理

从ADF4360-1外部输入的信号有标准频率源信号和控制信号,14位可编程参考R分频器对外部频率源信号分频后得到参考频率送至鉴相器。控制信号由时钟信号CLK、数据信号DATA和使能信号LE组成。在CLK的控制下,串行输入24位数据信号,暂时存放在24位数据寄存器中。在接收到使能信号LE后,先前输入的24位数据根据地址位到达对应的锁存器。

ADF4360-1的主分频比N由双模预分频器(P/P+1)、可编程5位A计数器及13位B分频器实现,算法为N=B×P+A,输出频率为:fout=(B×P+A)×fref/R,通过设置A,B,R三个控制字寄存器的控制字来实现对锁相环的控制。该芯片外围只需添加环路滤波器,根据输出频率大小选择合适的参数,即可输出较稳定的频率。

1.2 主要性能

ADF4360-1是美国ADI公司生产的一款高性能锁相频率合成芯片,主要可应用于无线射频通信系统基站(GSM,WCDMA)、手机以及通信检测设备中,为上下变频提供本振信号。其特性如下:

工作电压:3~3.6 V;输出信号功率可控范围具有四组可编程双模分频器8/9,16/17,31/32;三线串行接口进行编程控制;1.8 V逻辑兼容;输出功率可编程范围是-13~-6 dB;能够进行模拟和数字锁定检测;内部集成VCO;具有软件和硬件掉电模式。

2 系统的设计与实现

在中频发射电路中,本振源电路模块对整个系统的稳定性起着至关重要的作用。本文利用锁相频率合成芯片ADF4360-1设计2.33 GHz本振源信号,为射频发信机正交混频电路提供性能良好的本振载波。电路框图如图2所示。

2.1 电路参数设定

基于锁相环的基本原理,只需要在内部集成VCO的频率合成芯片ADF4360-1外围加环路滤波器,即可实现PLL频率合成电路。

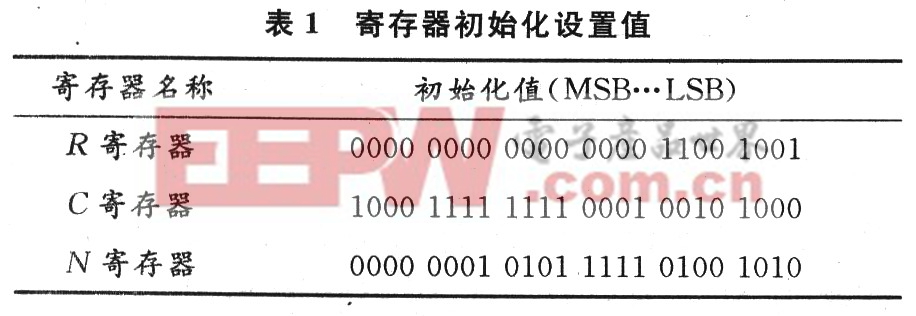

本电路设计中,ADF4360-1的PFD输入频率为200 kHz,因此参考时钟分频R=50。由公式fout=(B×P+A)×fref/R,可计算出N为11 250,双模前置分频器设置为P/(P+1)=32/33,计数器A设置为18,计数器B设置为351。根据ADF4360-1芯片资料,三个控制寄存器初始化设置为R寄存器0000C9H,C寄存器8FF128H,N寄存器015F4AH,如表1所示。本振源电路输出信号功率为-6 dB。

2.2 环路滤波器电路设计

环路滤波器(LPF)具有低通特性,它主要是抑制鉴相器输出电压中的载频分量和高频噪声,降低由VCO控制电压的不纯而引起的寄生输出。更重要的是它对环路参数调整起着决定性的作用。

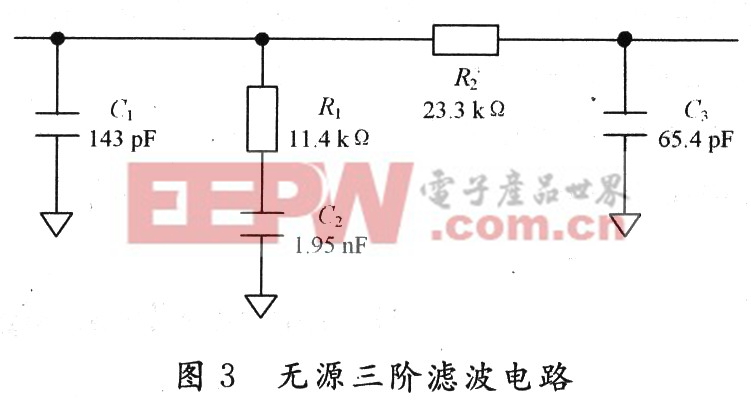

利用AD公司提供的专用设计与仿真工具软件ADI simPLL对图2结构形成的无源三阶滤波电路进行仿真、设计。依照软件提示,逐步设定各项参数,并选择芯片型号和环路滤波器形式,最后生成的电路如图3所示。

2.3 锁相环本振源电路设计

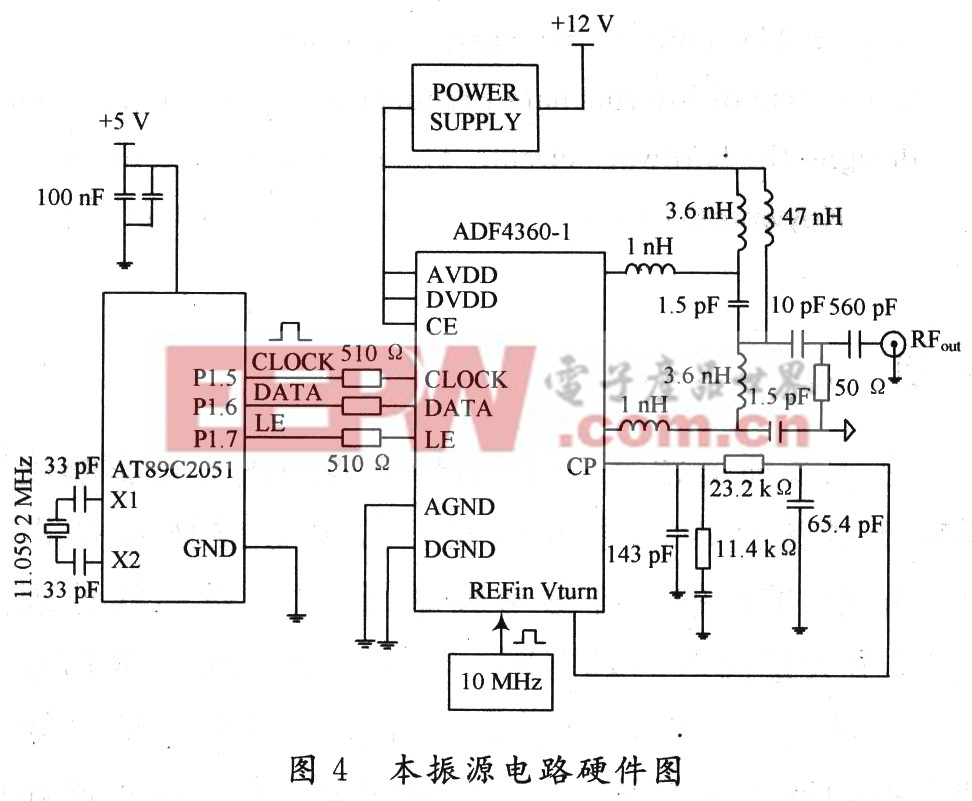

完整的硬件原理图如图4所示。

电源电路采用TPS76333和LM317T产生稳定的3.3 V电压供电。ADF4360-1的参考时钟输入引脚与晶振电路输出端相连,在内部VCO输入引脚VTUNE与内部电荷泵输出引脚CP之间接入三阶环路滤波电路。

核心芯片内部控制寄存器的初始化数值通过单片机控制写入,单片机采用ATMEL公司的AT89C2051。

3 编程控制及目标寄存器初始化

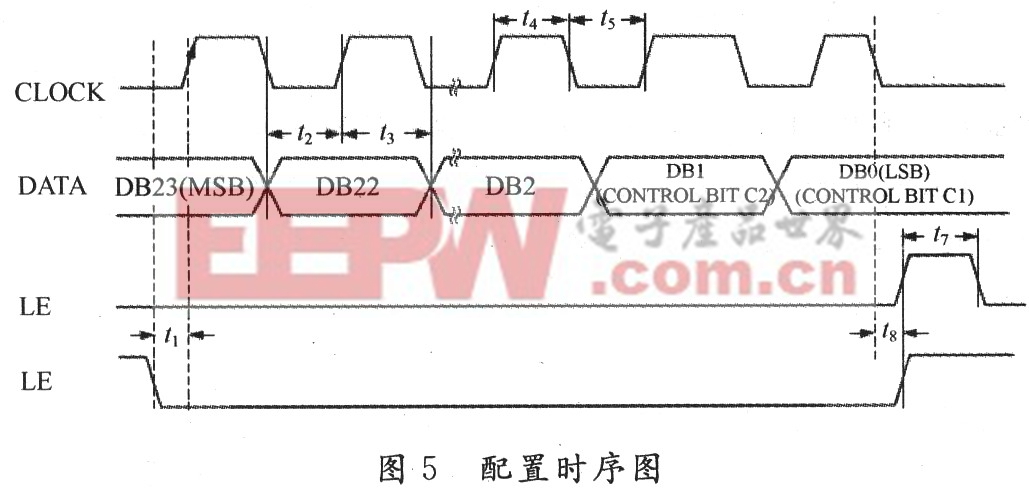

单片机P1.5,P1.6,P1.7三个I/O口分别与芯片CLK,DATA,LE相连。图5给出了数据输入的时序图。数据(DATA)在每个时钟(CLOCK)的上升沿从MSB(最高有效位)开始依次写入24位移位寄存器中,直到LSB位写入完成之后,由来自LE的上升沿将存储在24位移位寄存器中的数据一次性锁存入目标寄存器(包括R计数锁存器、N计数锁存器、功能锁存器以及初始化锁存器),再进行下一个目标寄存器的初始化。寄存器赋值顺序为R-C-N,目标寄存器的选择由移位寄存器最末两位DB0,DB1来决定,其中C和N寄存器的赋值时间间隔应大于5 ms。

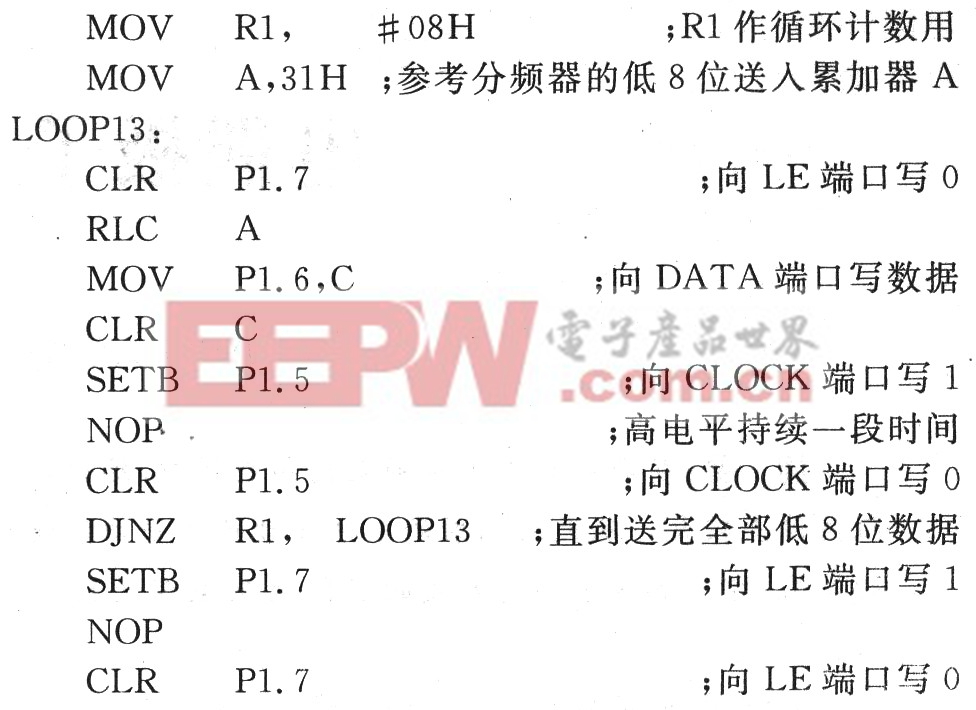

单片机控制程序(R寄存器)如下:

|

|

4 结 语

本文介绍了利用锁相频率合成芯片ADF4360-1为中频射频发信机设计本振信号源,给出了设计的关键参数、控制流程以及部分程序代码。最后测得相位噪声为-83 dBc/Hz@1 kHz,达到了基本标准。由于ADF4360-1内部集成VCO、外部通过单片机I/O口写入控制字,因此该系统具有外围电路简单、调试方便、功耗和成本低等特点,可广泛应甩于射频电路系统以及无线通信系统中。

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)

- 无线通信网络设计与现场测试(10-10)

- WiMAX数据传输加密方案设计与实现(05-25)

- 高性能TD-SCDMA接收机的设计(03-15)

- 初步设计WiMAX射频系统(03-29)