简化嵌入式视频接口

常见工业视频应用面临的难题

我们首先来检视一下几种常见的应用。机器视觉系统需要将捕获的图像数据从数码相机传输至远程帧捕获器。数据传输速率受图像捕获的分辨率、位深度及帧速率影响。设计较高的分辨率与位深度的图像,是为了提供进行复杂分析所需的细节数据。这对于因几何图形缩小而需要进行更精密检测的电子检查设备等应用至关重要。要提高整体的检查传送率,则需要更快的帧速率。

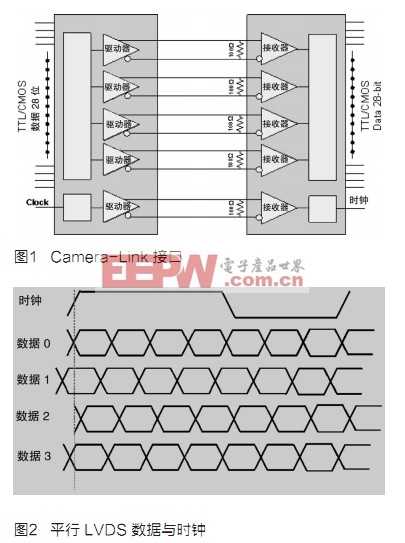

如今的机器视觉系统通常采用由 Camera Link 标准制定的通信接口。这个重要标准发表于 2000 年 10 月,多年来一直成功地为视觉行业提供支持。此接口由串行化数据(7:1 比率)的平行差动分对以及平行差动频率组成。图 1 所示为常见 Camera-Link 接口。

采用低电压差分信号传输 (LVDS) 的 7:1 串行方案,可为许多应用提供高效、强大的通信能力。但若将该技术扩展至较高吞吐量与较长距离,则存在一些限制和难题。当时钟速率提高和距离增长时,差分时钟与数据对的平行性质就容易受影响从而使配对之间的过长电缆发生偏斜。由于在相机链路的接收器端是使用独立时钟通道对数据进行采样的,因此保持正确的设置以及两者之间的关系非常重要。随着互连长度增加,对间偏斜也会增加,甚至可能会超过限制。为了将偏斜减至最小,可能需要高级且更贵的电缆与连接器。

在工业显示器系统中,影像来源(成像器或图形控制器)与数字显示器之间的链路也面临着类似的难题。如同视觉系统一样,工业显示器系统使用驱动器来提高数据速率,并且支持高达真彩色(每个像素 24 位)的较高色彩深度。更为明显的发展趋势是高清 (HD) 甚至更高分辨率的应用,这些影像可为监控及医疗应用提供有用的细节。平行 LVDS 解决方案(类似于 Camera Link 使用的解决方案)具有同样的电缆偏斜限制。随着数据速率提高,偏斜要求的限制会进一步减小,最大电缆长度也因此缩短。

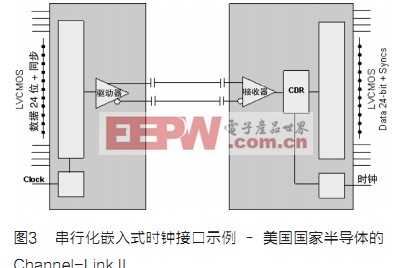

使用嵌入式时钟接口可以消除配对之间的这种偏斜限制。所有数据与时钟经过编码和串行化后,将通过单一差分对进行传输。解串器接收串行流,然后使用时钟与数据恢复 (CDR) 电路提取时钟与数据信号。

除了解决偏斜问题外,串行化解决方案还具有多个其它方面的优点。仅驱动一个差分对可减小互连媒体的整体大小。这意味着可以使用较小的电缆与连接器,将 PCB 上的连接器覆盖面积减至最小,并使接口变得更狭小且更具弹性。减少电缆组件中的配对数量,以及消除对严格偏斜容错的限制,将允许使用较低成本的电缆。

转移至串行化接口对系统设计具有非常积极的影响。但是,在使用嵌入式频率方案进行设计时,必须考虑一些因素。首先要考虑的是差动对上的数据速率现在比较高。过去通过四个配对来传输的数据,现在仅通过一个配对进行发送,因此数据速率大约提高了 4 倍。

简化设计的技术我们现在来探讨一下与较高接口速度相关的一些考虑因素,以及可用于简化设计和提供强大且具有成本效率的解决方案的各种功能与技术。

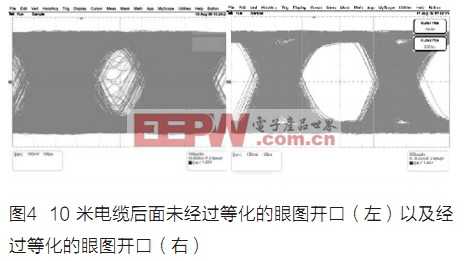

在这种较高的数据速率下,信号完整性显得尤为重要。我们将不再关注时钟与数据的一致性,而是关注串行化数据流内每个位的眼图开口。在数据穿越电缆时,信号会因衰减、抖动及符号间干扰 (ISI) 效应而降级。要正确接收信号,重要的是电缆末端(解串器输入端)的数据眼必须是“打开”状态。

电缆等化与去加重是专用于防止信号降级的两大功能。等化的作用是“重新开启”电缆最末端差动信号的数据眼。均衡器采用高通滤波器,以及与电缆衰减曲线成反比的增益曲线。可对均衡器增益进行编程的能力,允许通过不同电缆与长度来进行效能优化的微调。此电路可以是分离式电路,或是内置于解串器输入端。

第二项技术是信号波形还原,可防止符号间干扰 (ISI) 效应。依据正在传输的数据模式,电荷可能会累积在电缆上。这会妨碍快速切换至相反状态的能力。ISI 会导致信号振幅降低,这种情况在发送单一位(如由零组成的一个长字符串正中间的“一个”位)时尤为

- 松耦合变压器的ANSYS三维仿真设计(07-11)

- GapSense软件 避免无线信号干扰(04-23)

- R&S GNSS仿真器提供真实环境测试情境(07-30)

- 改进型Wilkinson功分器的设计(10-14)

- NSN增强Band 41 TD-LTE基站传输功率和容量 (11-12)

- ANSYS发布ANSYS15.0 新版本将促进结构和电磁仿真技术的发展(12-16)