DBF系统的数字正交相干检波设计

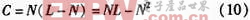

应点乘,需要N(L-N)次乘法,c段与a段相同,亦为N(N-1)/2。实际应用中,a段与c段作为暂态通常忽略不计,所以整个低通滤波器的卷积运算量就可以简化为

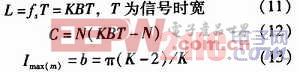

在满足滤波器性能的条件下,滤波器应以运算量最小为目标,当采用满足式(7)的fs(令fs=KB)时,L、C和Imax(m)可表示为

式(12)可以确定滤波器通带,阻带和过渡带的参数。在满足式(7)的条件下,显然fo越大,所需fs越大,过渡带Imax(m)越宽,中频滤波器实现越容易,所需阶数的折叠损耗越少。

滤波器的阶数N与过渡带的宽度以及通阻带纹波成反比。N越大,则可使过渡带越窄,纹波通阻带纹波越小,滤波器的性能相应就越好,越逼近理想滤波器。但是滤波器的延迟、暂态长度、复杂度也会增大,前者影响实时性,中者形成处理盲区,后者增加运算量。

3 工程实现

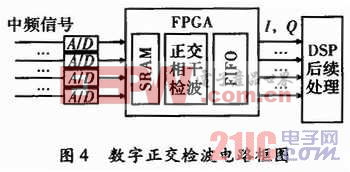

本系统为16通道的数字多波束天线系统,天线可接受信号的带宽为7 MHz,需要使用3个编码信号对3个目标完成测向、定位、数据传输,其中心频率分别为f10=9.15 MHz;f20=10.9 MHz;f30=12.6 MHz并且带宽均为1 MHz,信号总带宽为B=5.45 MHz。其中数字正交检波的电路框图,如图3所示。把4路作为一组,这样系统就有4组结构完全一样的框图组成。4路中频信号由ADC采样进入集成3个模块的FPGA,充分利用了FPGA计算速度快、可自定义的引脚多等特点,降低了系统成本,减少了器件面积,最后正交相干检波后的4路I、Q信号分时送入DSP作后续处理。

4 计算机仿真

在进行计算机仿真时,使用3个线性调频,时宽均为T=124μs信号,其中滤波器设计采用窗函数设计法。

试验1 由式(6)可得过渡带宽I(fs,m)随采样频率的变化如图4所示,采样频率的取值范围为[13.65,16.3]∪[27.3,+∞],单位MHz,满足式(7)的fsopt=14.533 MHz,此时I(14.533,2)=1.217 7。表1为各种窗函数设计的40阶FIR滤波器对应的IR,考虑过渡带带宽和阻带衰减,采用80 dBChebwin窗。表2为不同滤波器阶数所对应的运算量C,考虑本系统FPGA可利用的资源和处理速度,采用40阶FIR。表3为采用80 dB Chebwin窗、40阶FIR滤波器时各频点的IR,可知在整个频带内都有较好的IR。

试验2 在确定系统各个参数后,图5为采样后带通信号频谱以采样频率fs为周期沿拓,图6为解调后信号频谱,原带通信号变为基带信号。图7为采用窗函数设计的低通滤波器幅频特性。图8为镜频被抑制掉,原实信号变为了复信号。图9为任一个chirp信号均可以与原带通信号进行脉冲压缩,表明正交鉴相过程中信号包含的信息没有丢失。

5 结束语

5 结束语

结合某DBF系统论述了正交相干检波过程原理,总结了其中的优化设计,仿真结果对其他的应用也具有一定的参考价值。

- 基于软件无线电的通用数字解调方案研究(04-17)

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)

- 无线通信网络设计与现场测试(10-10)

- WiMAX数据传输加密方案设计与实现(05-25)

- 高性能TD-SCDMA接收机的设计(03-15)