智能卡控制器IP核的设计与实现

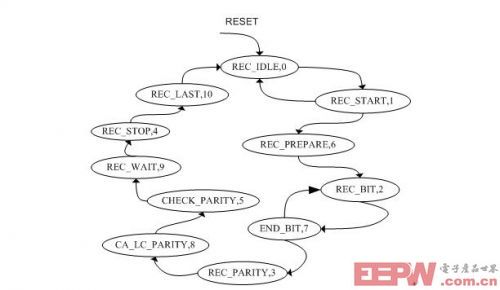

何实现Receiver Shift的逻辑电路,下图是本智能卡控制器数据接收模块中有关Receiver Shift逻辑电路的主控状态转换图:

图2 接收模块主控状机

该状态机共有十个状态,其中主要状态是:状态1(REC_START)用来探测数据的起始位Start;状态2(REC_BIT)用来接收数据ba到bh,组成一个字节;状态3(REC_PARITY)用来接收数据的奇偶校验位;状态4(REC_STOP)探测Stop位。

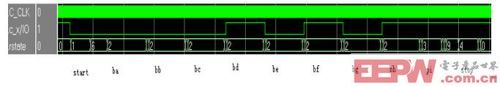

下面是该状态机控制有关逻辑读入数据的仿真波形图:

图3 接收一个字节数据的状态变换波形图

图3 接收一个字节数据的状态变换波形图

4.2、数据发送模块

同样, 对于发送模块的设计,主要问题也是如何实现Transmitter Shift的逻辑电路,下图是本智能卡控制器数据发送模块的主控状态转换图:

图4 发送模块主控状机

该状态机共有五个状态:状态1(SEND_START)用来发送数据的起始位Start;状态2(SEND_BYTE)用来发送数据ba到bh;状态3(SEND_PARITY)用来发送数据的奇偶校验位;状态4(SEND_STOP)发送Stop位,最后状态机转入空闲状态0(SEND_IDLE)。

下面是该状态机控制有关逻辑发送数据的仿真波形图:

图5发送一个字节数据的状态变换波形图

4.3、函数模块

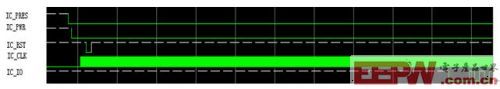

函数模块可以在软件控制下产生激活智能卡和关闭智能卡所需的相关时序。这里简单介绍一下本控制器在软件的支配下,激活智能卡的过程,见下面的波形图。

图6激活智能卡时的波形图

在该波形图中,信号IC_PRES首先变低,表明有智能卡插入。接着智能卡控制器通过IC_PWR打开智能卡的电源。待电源稳定后,智能卡控制器通过IC_CLK向智能卡输出时钟信号。同样,在时钟稳定后,智能卡控制器通过IC_RST向智能卡输出复位信号。最后智能卡控制器在数据信号IC_IO上探测到智能卡复位应答(ATR,Answer to Reset),这样就完成了智能卡的激活工作。

5.结论

本方案所设计的智能卡控制器IP核,采用Verilog HDL语言,以较少的硬件代价,在本公司研发的硬盘数据加密芯片中,成功实现了对智能卡密钥的读写控制,并且该方案具有较强的灵活性,可以方便地移植到其它嵌入式应用系统中,具有较高的使用价值。

ASIC ISO7816 智能卡 IP核 Verilog 语言 相关文章:

- 专用集成电路实现宽带射频相控阵波束形成(06-26)

- 基于FPGA水磁无刷直流电机控制电路(04-28)

- 在系统设计中的如何选择半导体器件:ASIC,还是FPGA?(05-29)

- LEON2应用于DCPU的FPGA仿真(05-11)

- 射频产品如何从设计轻松过渡到制造(07-15)

- HDB3编码器ASIC的设计(06-15)