智能卡控制器IP核的设计与实现

1、引言

随着信息技术的飞速发展,越来越多的地方要求对用户身份的识别以及重要数据的安全存储。而智能卡(SmartCard)又称集成电路卡(Integrated Circuit Card 即IC卡),是具有高的可靠性安全性和灵活性的数据承载设备,现已被广泛应用于政府、金融、电信、交通及公共事业等领域。

智能卡控制器是连接智能卡和主控设备的桥梁,由于智能卡的应用不断增加,越来越多的SOC芯片内嵌了智能卡控制器IP核。这种基于IP核的设计方式已成为IC设计的主流,这里主要介绍智能卡控制器IP核的数字逻辑实现方法以及其在硬盘加密芯片中的应用。

2、协议简介

这里仅对本文中要用到的部分协议内容作简要说明,详细的协议内容请见参考文献1。

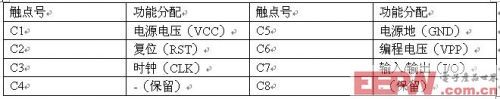

智能卡共有八个触点,其中有用的就C1、C2、C3、C5、C6、和C7六个触点,具体见下表:

表1:智能卡触点

智能卡控制器是通过智能卡触点C7(I/O)与控制器进行半双工串行通信的,在每一时刻触点C7只有状态Z和状态A两种状态。

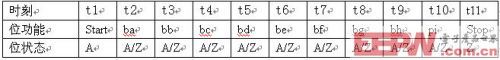

智能卡要传输一个字节(8个Bit)数据的要11个Bit位的时间宽度,在下表中被记成t1到t11。其中第一个时刻t1传输的Start位被称为起始位;第二到第九个时刻,即时刻t2到时刻t9,传输的数据ba到bh为一个字节的八个位;时刻t10传送的pi位为奇偶校验位;最后一个时刻t11传输的Stop位被称为停止位,标志着一个字节(8个Bit)的数据传输完成。请见下表:

表2:智能卡串行传输数据格式

表2:智能卡串行传输数据格式

3、微体系结构

3.1、接口信号

该IP核接口主要分为CPU总线接口、中断信号和智能卡控制接口,这里主要介绍一下有关智能卡控制的接口信号,即连接或控制智能卡上有效触点的信号,它们为:

1)智能卡是否存在信号IC_PRES:用于探测智能卡座上是否有智能卡存在,当有智能卡插入或拔出时,该信号的电平发生跳变,本IP核能够探测该信号的电平的变化,并以中断等方式报告给CPU;

2)智能卡电源控制信号IC_PWR:用于控制智能卡的电源VCC或VPP(触点C1或C6),用于打开和关闭智能卡电源;

3)时钟信号IC_CLK:同智能卡触点C3相连接,用于向智能卡输入一定频率的时钟信号;

4)复位信号IC_RST:同智能卡触点C2相连接,用于向智能卡发出复位信号;

5)双向串行数据信号IC_IO:同智能卡触点C7相连接,用于实现与智能卡的双向数据通信。

3.2、模块和功能

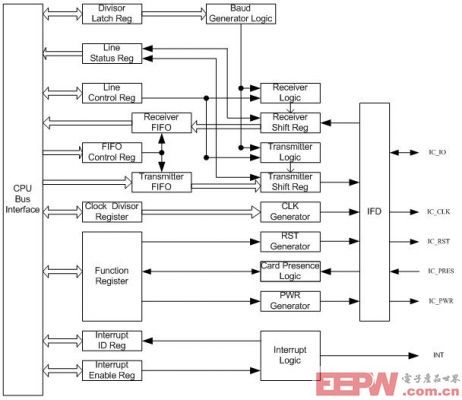

智能卡控制器核内部有发送和接收模块(Transmitter and Receiver)、中断仲裁模块(Interrupt Arbitrator)、函数模块(Function Generator)、时钟模块(Clock Generator)、智能卡接口模块(Interface Device)和访问寄存器模块(Register Access Control)六大模块,这些模块之间的关系见图1所示:

图1ISO7816智能卡控制器模块结构图

主要模块功能及特征描述如下:

1. 发送和接收模块

发送和接收模块负责处理数据帧的发送和接收。发送模块是将FIFO发送队列中的数据按照设定的格式把并行数据转换为串行数据帧,并通过发送端口送出去。接收模块则监视接收端信号,一旦出现有效开始位,就进行接收,并实现将接收到的异步串行数据帧转换为并行数据,存入FIFO接收队列中,同时检查数据帧格式是否有错。智能卡控制器的帧结构是通过LCR(Line Control Reg)寄存器设置的,接收和传送器的状态被保存在LSR(Line Status Reg)寄存器中。

2. 中断仲裁模块

当任何一种中断条件被满足时,并且在中断使能寄存器(IER, Interrupt Enable Reg)中相应位置1,那么智能卡的中断请求信号INT被置为有效状态。为了减少和外部软件的交互,智能卡控制器把中断分为四个级别,并且在中断标识寄存器(IIR, Interrupt ID Reg)中标识这些中断。四个级别的中断按优先级级别由高到低的顺序排列为:智能卡插拔中断、接收线路状态中断、接收数据准备好中断和传送拥有寄存器为空中断;。

3. 函数模块

该模块产生智能卡的相关时序。通过向函数寄存器(FR, Function Register)相应的位置入相关的参数来探测智能卡、管理电源和产生复位时序等。

4. 时钟模块

时钟模块产生相应频率的时钟供给智能卡,时钟的频率由CPU总线的时钟频率和写入时钟分频寄存器(CDR, Clock Divisor Register)的值来决定,关系表达式如下:

fIC_CLK = fCPU /(2 * CDR)

5. 智能卡接口模块

该模块将相关信号进行适当的调整,以便适合于IC智能卡的通信。

6. 访问寄存器模块

当智能卡控制器被总线控制器选中时,CPU可通过读或写操作访问被地址线选中的寄存器。

4、设计实现

这部分将对本智能卡控制器中主要模块的数字逻辑的实现方法逐一作简单说明。

4.1、数据接收模块

在设计接收模块的过程中,关键是如

ASIC ISO7816 智能卡 IP核 Verilog 语言 相关文章:

- 专用集成电路实现宽带射频相控阵波束形成(06-26)

- 基于FPGA水磁无刷直流电机控制电路(04-28)

- 在系统设计中的如何选择半导体器件:ASIC,还是FPGA?(05-29)

- LEON2应用于DCPU的FPGA仿真(05-11)

- 射频产品如何从设计轻松过渡到制造(07-15)

- HDB3编码器ASIC的设计(06-15)