一种改进的扩展RC-LDPC码校验矩阵构造方法

时间:07-19

来源:互联网

点击:

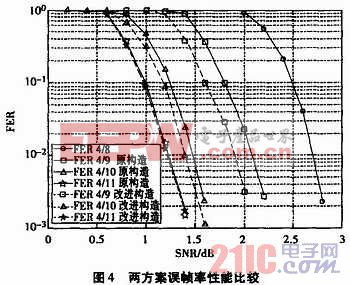

图4为改进的构造方式与原构造方式误帧率比较。通过仿真可以看出,改进的构造方式的误码性能有了明显的提升。在码率为4/9时,改进的RC-LDPC校验矩阵构造方式性能上大约有0.15 dB提升,而在码率为4/10时,改进的构造方式比原来的构造方式大约有0.07 dB提升。两码率性能提升的不同是因为随着扩展校验比特的增加,译码时的码字与原方案译码时的码字在信息节点度数上的差异越来越小造成的。随着码率的继续增大,两种方式译码时在信息节点度数的差异将消失。从仿真中看出,在RC-LDPC的最小码率情况下,误帧率基本相同。

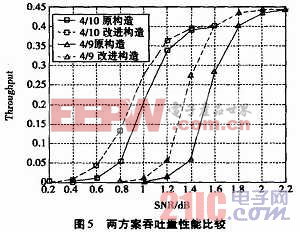

图5为改进的构造方式与原构造方式吞吐量性能比较。仿真中采用的是IR-HARQ系统,码率为4/11时,两方案的误帧率基本相同,所以只对码率为4/9、4/10时的吞吐量进行分析。从图5,改进的方案在吞吐量上要优于原构造方式。随着信噪比的增加,误帧率变得越来越小,两方案的吞吐量会慢慢汇合在一起,最终两种方案的吞吐量会相等。但是不同的码率的吞吐量最终值不相同,当信道足够好时,吞吐量在数值上等于码率。

4 结论

本章首先简要介绍了一种具有Z字型结构的校验矩阵H的构造方法。之后基于非规则LDPC码中不同度数的信息节点对性能的不同影响的特点,提出了一种改进的校验矩阵构造方案。同时针对Z字型结构的校验矩阵H构造方法中容易引入4环的不利因素,提出了一种消除4环的方法。通过仿真情况来看,对于部分扩展码率,误码性能和吞吐量性能都有不同程度的提升。

构造 方法 矩阵 校验 扩展 RC-LDPC 改进 相关文章:

- 具有较大围长的正则LDPC码构造方法介绍(12-24)

- SFH506-38与RPM-638红外接收头构造分析(08-11)

- 一种具有较大围长的正则LDPC码构造方法(03-15)

- GSM/UMTS手机的检验和最终测试方法(09-07)

- 多种Wi-Fi定位方法对比 移动领域选谁(09-17)

- 轻轻松松让你学会阻抗匹配原理和方法(06-28)