25G高速无源通道的设计挑战

连接器的串扰建模不易。一般连接器厂商给出的S参数或Spice模型仅局限于连接器的本身,当装配到PCB(如背板)以后,模型的精确建立和修正将形成挑战。材料特性、几何尺寸、是否背钻和过孔加工精度都将成为决定性因素。而当串扰模型被比较准确地建立起来之后,又将出现另一个挑战,那就是多通道码型信号的生成。要生成各种不同长度的码型,以及确定是否带有噪声和抖动等压力信号,需要不停地改变或扫描不同通道之间的相位、偏斜和延迟,以找出串扰的最坏情况。

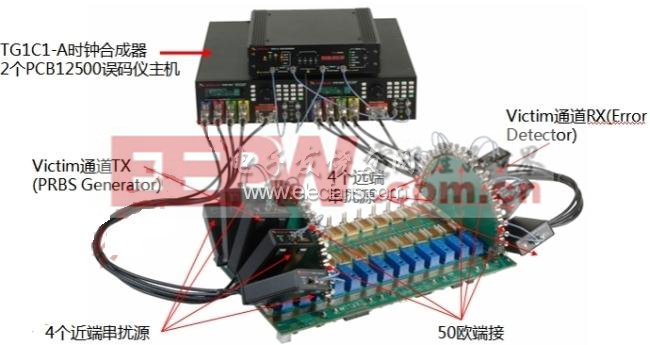

除了仿真,也可以测试实际链路中的串扰,这样也能验证仿真的正确性。对于串扰的测试,传统上采用VNA或TDR来测试物理结构上的串扰,但所测得的串扰大小与数据无关。也就是说,无论是VNA测试出来的串扰幅度,还是TDR测试出来的串扰最强耦合位置,均不能直接指示出是否引起了误码或眼图的恶化。要测试数据的相关串扰,需要借助并行通道误码仪(图7)。由于该设备可以级联,所以能够测试多达8个以上干扰通道的情况。

图7:对于一个典型的背板,配置了4个近端串扰和4个远端串扰,并监测受害通道的误码和浴盆曲线。

图7所示的配置可以将数据相关的串扰很好的表征出来,包括改变码型发生器的幅度和去加重,得出浴盆曲线,从而找出串扰对数据的最坏影响以及减少串扰和抖动的办法。兴森快捷高速实验室已利用此设备多次帮助客户成功地设计出了高速背板并通过了验证。

本文小结

当高速串行信号速率急速增进到25Gbps后,发射端和接收端的信号处理将更加复杂。由于传输的信号仍然是NRZ 码型,发射端采用3抽头(tap)的预加重,接收端采用3抽头以上的CTLE和DFE两级均衡来克服通道上的损耗。而要最优化配置发射端和接收端的均衡,则需了解到通道的损耗情况。设计者只需要考虑到影响损耗的各种因素,做好充分的仿真和测试,便可以做到通道可控,包括大家所熟悉的阻抗控制、损耗控制和串扰控制。设计出的通道不仅要满足规范,而且还要留有充足的裕量。这样不仅不会给有源部分造成压力,而且还会为未来的速率扩展和升级留下余地。

- 5G的挑战:从Sub-6 GHz到毫米波系统(05-16)

- 大数据时代的挑战和LTE部署策略(12-07)

- 路由器也要实现无线化 WiFi挑战7Gbps无线传输(06-20)

- 宽带WPAN接入带来的机遇与挑战(04-11)

- 如何应对数据中心管理的挑战(03-25)

- 直接变频接收机设计可实现多标准/多频带运行(10-11)