基于高性能AD9640的抗干扰无线接收机设计

机PCB排版布线的总体要求如下:

● 所有电源在PCB板顶层或/和底层应留出散热区[4];

● 所有盒子输入输出接口位于PCB板的底层;

● PCB板顶层和底层大面积敷铜并接地;

● 电源及其附属元件靠近,独立驱动电源平面,电源平面为电源分配网络。元器件供电从电源平面获取,根据需要在靠近管脚处滤波;

● 所有电源线进入盒子安装“穿心电容”;

● 放大器直接接地,同时应该屏蔽所有高增益放大器以防止它们产生振荡。

ADC布线

在PCB原理图中,模拟地的网络标号为AGND,数字地的网络标号为GND。在将A/D转换器的模拟地和数字地引脚连接在一起时,大多数的A/D转换器是将AGND和DGND引脚通过最短的引线连接到同一个低阻抗的地上,任何与DGND连接的外部阻抗都会通过寄生电容将更多的数字噪声耦合到芯片内部的模拟电路上。从而需要把A/D转换器的AGND和DGND引脚都连接到模拟地上,但这种方法会产生诸如数字信号去耦电容的接地端应该接到模拟地还是数字地的问题。

本设计的多通道接收机中A/D转换器较多,如果在每一个A/D转换器的下面都将模拟地和数字地连接在一起,则产生多点相连,模拟地和数字地之间的隔离就毫无意义。而如果不这样连接,就又违反了厂商的要求。因此,最好的办法是开始时就用统一地,将统一的地分为模拟部分和数字部分。这样的布局布线既满足了ADC器件厂商对模拟地和数字地引脚低阻抗连接的要求,同时又不会形成环路天线或偶极天线而产生电磁兼容(EMC)问题。本文中AD9640的PCB制版安排见图3。

接收机排版布线

本设计中,接收机布线坚持2W原则:布线宽度为W,线间距不小于2W。PCB电路板分为模拟层和数字层两个部分,共12层,制版安排见图2,布线安排设计如下。

(1)模/数布线和元件排版分离。高速信号位于优质布线层clk-digital component和signal_1,高速信号线同低速信号线尽量远离,重要的低速信号线位于低速信号层signal_2 和signal_3。首先,保证关键高速时钟和信号线布放于层clk-digital component和signal_1;然后保证关键低速信号线位于层signal_2 和signal_3;其次,低速信号线进入高速布线层clk-digital component时应该远离高速信号线(尤其是时钟),高速信号线进入低速布线层signal_2 和signal_3应该远离低速信号线;最后,上述原则无法实施时应该增加布线层。

(2)PCB板下三层为模拟电路,上七层为数字电路;层clk-digital component布线64MHz时钟;层signal_1布线64MHz数字信号,包括AD9640采样64MHz高速数字信号;层signal_2 和signal_3布线小于64MHz的所有其它数字信号;将数字地GNDdigital2用多个过孔连接到GNDdigital1上,GNDdigital2仅仅为隔离模数两个系统,保护模拟信号免受数字干扰。GNDdigital1作为电源+5V的数字地;GNDdigital2作为+1.8V、+2.5V、+3.3V的数字地。

(3)FPGA、稳压片等所有核心元件位于顶层clk-digital component。

(4)各层敷铜接地方法:

● 层clk-digital component、signal_1、signal_2 、signal_3的大面积敷铜,并通过多个过孔连接到GNDdigital1;

● 层analog component的大面积敷铜,并通过多个过孔连接到GND analog。

(5)电源布线:电源线根据使用区域大面积填充,形成分割的电源平面。模拟电源平面PWRanalog分割为3.3V和5V两个部分,数字电源平面PWRdigital分割为1.8V、2.5V、3.3V、5V四个部分。

实物制造及测试

图4示出所设计的接收机实物图,将其放置在一定的温度、湿度和振动压力之下测试以检查任何设计或工作的缺陷。

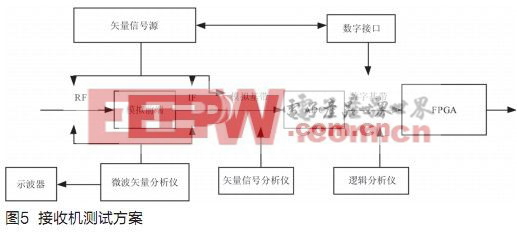

在本文设计接收机的调试过程中,用到仪器为:数字接口(Agilent N5102A),矢量信号源(Agilent E8267D),微波矢量分析仪(Agilent 89650A),示波器(Tektronix TDS 3032B),矢量信号分析仪(Agilent 89611A),逻辑分析仪(Agilent 16900A)。上述仪器,对接收机测试的连接图如图5所示。

矢量信号源产生接收机需要的各种调制信号输入到射频前端,经过测试可得,接收机体积小,性能稳定,且便于调试,实际ADC采样速率为63.488MHz;进入FPGA数据速率为7.936MHz;FPGA处理主时钟速率为63.488MHz; 2~30MHz带宽、-113dBm~-36dBm的通信信号被接收的平均误码率为:Pe10-5。因此,本接收机射频前端抗干扰性强,电磁兼容性好,满足设计要求。

接收机 设计 无线 抗干扰 高性能 AD9640 基于 相关文章:

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 高性能TD-SCDMA接收机的设计(03-15)

- 卫星接收机在微波传输中的再利用(07-27)

- 基于FPGA的短波通信接收机(11-19)

- DM500S接收机的另类用途(01-20)

- 亚运在深圳系列之三:从生产线到研发部(11-14)