基于高性能AD9640的抗干扰无线接收机设计

在无线接收机射频前端硬件的实际制作中,中频频率的选择、带通滤波器的中心频率与3dB带宽、外部无源器件的使用等设计考虑,都需要随着不同的系统应用而仔细的规划与调整,以便在适当的成本下达到规定的性能。本文以认知抗干扰为设计目标,主要讨论了接收机链路的核心器件之一—高性能的ADC,叙述它们如何满足对高性能的需求。此外,接收机系统的设计还包括器件的选择和设计,整体排版布线以及调试过程等步骤。

ADC设计

天线接收到的射频信号必须经过A/D数字化,以便后面的数字处理芯片进行数字信号处理[1]。ADC影响接收机体系的功耗、工作频率动态范围、接收带宽和总体成本,其性能更是能够影响接收机结构的设计。理想情况下,在接收机的链路天线后直接进行数据转换,ADC对射频信号直接进行抽样,这样很大程度上绕过了模拟器件。而本文接收机体系结构的一个重要特点是将ADC尽量靠近射频前端,在较高的中频直接进行数字化,因此A/D设计是接收机设计的核心之一。

选定最优采样频率

如果对采样输出信号进行滤波的低通滤波器可以做到矩形系数为1,在无混叠的采样率范围内选定任何一个频率都是可以的(不考虑采样时钟的抖动)。但是实际上,这样的滤波器是做不出来的,即使是矩形系数接近于1的低通滤波器也很难实现。如果后续的低通滤波器在过渡带里面没有频谱的平移转换,那么,即使矩形系数大一些也不会改变原信号的频谱结构,这也就意味着平移频谱之间的间隔应该越大越好。对于无混叠的采样率来说,并不是频率越高间隔越大,频谱间隔最大的无混叠采样率在降低后续低通滤波器的设计难度上是最优的。

本文首先讨论无混叠采样率与平移的频谱间隔的关系,然后结合方案选择一个最优的采样频率。

对图1中虚线所示的频谱块,其左间距表示为:

-fH+(m-1)fs-[fH-(m-1)fs]=2(m-1)fs-2fH (m=1, 2, 3…)

右间距表示为:

fL-(-fL+mfs)=-mfs+2fL

使频谱间隔最大条件是频谱块的左间距等于右间距:

2mfs-2fH=-mfs+2fL

即

![]()

比如天线接收的信号是75MHz中频,带宽1MHz的信号,所以使频谱间隔最大的采样频率为:fs=133.3333、66.6667、33.3333、26.6667MHz…(m=1, 2, 3, 4…)。注意,上面所指的频谱间隔最大是对于相应的m而言的,对于不同的m来说,间隔的绝对值随m的增大而减小。

由于超过100MHz的高精度A/D器件价格昂贵,我们选择m=2,这时的无失真采样频率fs的范围是50.3333MHz≤fs≤75.5100MHz。同时考虑到ADC采样频率与中频滤波器的带宽之间必须满足一定的关系:

fs≥B+B×w

其中w是该中频带通滤波器的矩形系数,本文设为:w=3。此时,ADC采样通带不会发生混叠,但过渡带将会混叠,直到ADC采样频率增大到上式右边的两倍后,过渡带才不会混叠。从本质上看,还是会“混叠”的,但此时“混叠”的信号已被衰减得很微弱,比如衰减到比通带信号小70dB以上。

最后考虑到后续DDC器件进行速率转换后输出速率为8MHz(由于ADC和后续算法处理要求),采样得到的信号速率最好是2的整数倍,同时又考虑到采样时对信号频段确定和控制的方便,最优的采样频率选定为64MHz。这个采样频率产生的频谱间隔对后续滤波器的设计也是足够的。

器件选择

综合采样精度和速率的要求对ADC进行选择:16位的ADC可以达到大约96dB的信噪比,但是精度达到16位同时速度超过60 MHz 的ADC价格非常昂贵且不易购买到;14位的ADC可以达到大约84dB的信噪比,也可以满足要求,还可以买到速度更快的产品。本设计选择14位双通道A/D器件AD9640[2]进行采样。其主要性能为:可选最大采样速率80、105、125、150MSPS;采样精度14位;无杂散动态范围85dB@125MSPS;信噪比71.8dB@ 125MSPS;低功耗750mW@125MSPS。

其中采样速率的改变可通过改变输入时钟来实现,从而可实现在不改变硬件的情况下通过软件来扩展。

设计高性能ADC之前的“前端”或输入配置,是获取所需系统性能的关键所在。整个设计的优化[3]取决于许多因素,其中包括应用的特点、系统划分,以及ADC 的构架等。许多放大器都十分适合用于高速ADC 的前端电路。ADA4937 能被用于150MHz以下的频率;由于它能处理很大的输出共模电压范围,因此它的主要优势是应用于ADC 的直流耦合应用中。对于窄带或谐振应用,使滤波器与放大器的输出阻抗匹配,来消除ADC 的输入电容。通常使用一个多极点滤波器来消除感兴趣频率范围外的宽带噪声。

接收机PCB设计

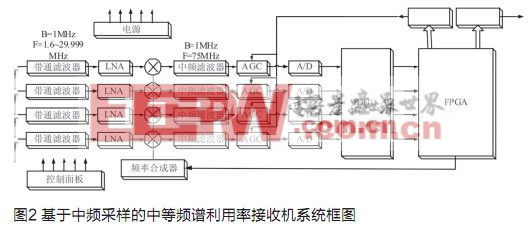

基于图2的接收机框图(图中DDC使用四通道数字下变频器AD6635)和PCB设计的基本要求,可以提出本文接收

接收机 设计 无线 抗干扰 高性能 AD9640 基于 相关文章:

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 高性能TD-SCDMA接收机的设计(03-15)

- 卫星接收机在微波传输中的再利用(07-27)

- 基于FPGA的短波通信接收机(11-19)

- DM500S接收机的另类用途(01-20)

- 亚运在深圳系列之三:从生产线到研发部(11-14)