扩频通信系统CCSK信息调制解调算法设计

进行相关运算以产生I、Q两路相关峰,再通过正交相关峰合成产生符号位为正的正交相关峰。图2所示为正交基带下变频信号处理电路原理框图。

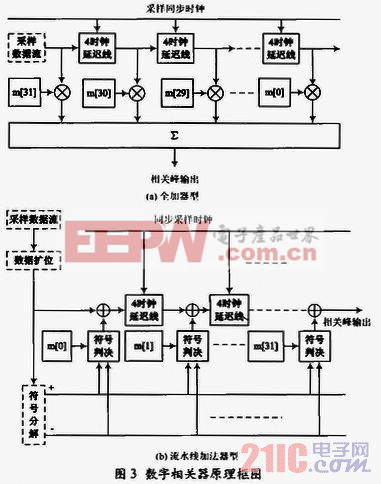

数字相关器是CCSK信息解调的关键部件,通过相关器进行CCSK信息解调有两种不同的逻辑电路架构,包括两级串联型相关处理算法电路和多极并行数字相关器。无轮哪种CCSK相关解调器,其核心都是数字相关器,而数字相关器分为全加器型数字相关器和流水线加法器型数字相关器。这两种数字相关器的原理框图如图3所示。

2.1 两级串联型CCSK数字相关器算法设计

两级串联型CCSK相关解调逻辑电路一般由两个全加器型数字相关器级联而成。如采用32 bit m序列扩频码的系统,可将两个32 bit相关器级联成64 bit相关器,其m序列本地码可设置成两个同样的m序列:

{a31,a30,a29,…,a2,a1,a0,a31,a30,a29,…,a2,a1,a0}

当输入基带码流信号为m序列的某一种32 bit循环移位码时,相关器就会输出相应的相关峰信号。其过程如下:

输入基带码流为32 bit m序列的原码时(时间次序为{a31,a30,a29,…,a2,a1,a0}),当码流与第一段本地码对应缓冲器内的本地序列{a31,a30,a29,…,a2,a1,a0}一致时,相关器就会输出第一相关峰;在采样同步时钟的驱动下,输入码流进入第二段本地码对应缓冲器内,此后,当码流与相关器的本地序列{a31,a30,a29,…,a2,a1,a0}一致时,相关器就会输出第二相关峰。

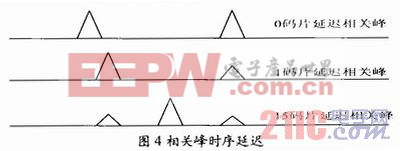

当输入信号是扩频码m序列的1次循环移位码时,只有当输入码流信号被驱动到{a30,a29,…,a2,a1,a0,a31}的位置上时,相关器才输出相关峰信号。相对于0次循环移位码产生的相关峰,其时序延迟了一个码片单位。依次类推,当输入信号是扩频码m序列的N(0≤N≤31)次循环移位码时,通常可以得到延迟N个码片时间的相关峰。图4所示是相关峰时序延迟示意图。

通过计算相关峰输出时间同基准(0延迟)相关峰之间的时间差,可以提取调制在信号上的信息数据N:

N=(数据相关峰字符时间-基准相关峰字符时间)/码片时间

采用两级串联型CCSK相关解调逻辑电路解调CCSK信息消耗的硬件资源较少,但由于要对相关峰进行定时检测以及消除部分相关峰,因此,对电路的处理时序较为严格,只能采用全加器型数字相关器来实现。而流水线加法器数字相关器由于不具有实时归零功能,无法实现两级级联,因此不适合两级串联型CCSK相关解调逻辑电路的相关器。

2.2 多路并行CCSK数字相关器算法设计

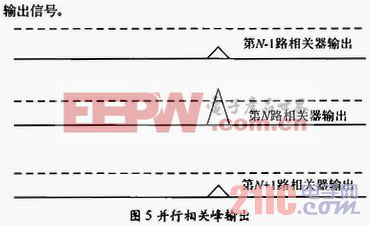

多路并行型CCSK数字相关器输入的的是m序列N次循环移位码,如32 bit系统中,m序列N次循环移位码有32种,接收方可以通过32个32 bit并行数字相关器对基带码流进行相关处理。当输入码流同第N路相关器的相关输出超出信号门限时,则认定接收到的数据为N,图5所示就是并行相关峰输出信号。

多路并行型CCSK数字相关器的电路结构比较简单,对电路时序的要求也较低,相关器输出时序位置固定,不需要进行时间差计算提取信息,也不需要对部分相关峰进行时序处理,故可采用对加法进位延迟要求较低的流水线加法器型数字相关器作为相关处理的核心部件。但是,多路并行型CCSK数字相关器消耗的硬件资源在同样码速率和码长时,比两级串联型CCSK数字相关器要多若干倍,因此,32 bit扩频系统中采用多路并行型CCSK数字相关器要比两级串联型CCSK数字相关器所消耗的资源多16倍。

3 结语

本文对CCSK信息的调制和解调算法进行了介绍,给出了CCSK逻辑编码电路的实时计算方法,同时对两级串联型CCSK数字相关器算法和多路并行CCSK数字相关器算法的设计进行了说明。采用直序扩频的通信系统具有较高的抗干扰能力,但通信信息速率会大幅下降。因此,在通信速率和抗干扰之间找到一个平衡点,是扩频通信系统的一个重要技术问题。而利用本文提出的CCSK编码解码技术可以有效地提高扩频通信系统的通信速率。

解调 算法 设计 调制 信息 通信 系统 CCSK 扩频 相关文章:

- 无线数传信号的发射和解调(07-18)

- MC3361+MCU的低速光纤通信模块设计(07-03)

- SDR是如何颠覆射频测试仪器的?(06-27)

- LTE-A PDSCH信道的解调技术研究与实现(06-28)

- 构建下一代802.11ac Wave3软件定义调制解调器(下)(03-01)

- 构建下一代802.11ac Wave 3软件定义调制解调器(中)(03-01)