构建下一代802.11ac Wave 3软件定义调制解调器(中)

接上篇

3 产品概述

CEVA RivieraWaves Stream 802.11ac Wave 3 软件定义调制 解调器 (SDM) 子系统是一种超高性能的 Wi-Fi 调制解调器, 支持更广泛的配置直到非常大的 MIMO 规格。

3.1 功能集

CEVA RivieraWaves Stream 802.11ac Wave 3 SDM 调制解调 器负责 MAC 接口和 ADC/DAC 之间所有的发射和接收信号 处理,包括无线控制和 AGC 控制。它支持以下功能:

? 大部分的 11ac 可选模式;

? 最高 256-QAM 的所有调制方案:MCS0-MCS9,一到 八个空间流;

? 1024-QAM 调制(MCS10 和 MCS11);

? 长保护间隔 (800ns) 和短保护间隔 (400ns);

? 用于提高链路可靠性,尽量减少散射、反射和折射效 应的空时分组编码 (STBC) ;

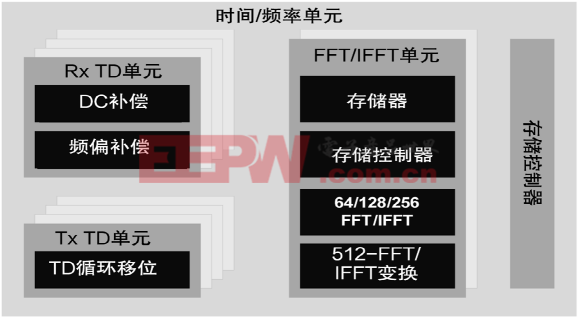

图3 时间频率单元架构

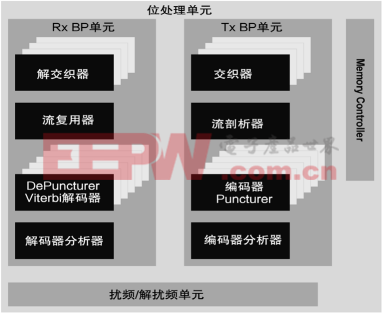

图4 位处理单元架构

? 与维特比译码器相比可将接收灵敏度提高 2 到 3 dB 的低密度奇偶校验(LDPC);

? 发射波束成形,作为一个波束成形器(beamformer)和一个波束成形接收端(beamformee);

? 多用户 MIMO (MU-MIMO)。

3.2 调制解调器子系统概述

CEVA Wave 3 SDM 调制解调器子系统采用混合设计,将 硬连线装置与 CEVA-XC 内核组合在一起,在尺寸和灵活性 之间实现了最佳平衡。它配备了参考控制和处理软件,组成 了一个功能完备的Wi-Fi 调制解调器。

此调制解调器将结合 CEVA Wave 3 Wi-Fi MAC 子系统和一个模拟/射频子系统,构成一个完整的 Wi-Fi 系统。

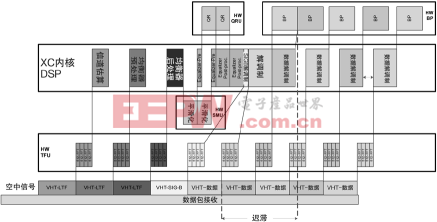

已选的一些调制解调器信号处理算法来与专门的逻辑 连用,因为它们对计算要求很高,而且不期望改变。但 DSP 内核上实现了所有关键的 Wi-Fi 调制解调器算法,并且从其 灵活性受益匪浅。CEVA Wave 3 Wi-Fi 调制解调器参考软件包

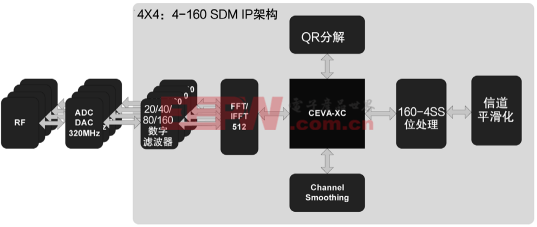

图5 4x4:4-160 架构概述

图6 时序图

含的复杂算法,该算法充分利用了 CEVA-XC 内核的功能强 大的矢量功能。关键算法编码在伪浮点数中,最大限度地减 少了实现损失,并保证了最佳性能。

软件使用寄存器和中断与硬连线单元进行通信。硬连 线单元和内核之间的数据交换通过一个基于存储器的专用互 连完成,而该互连使用 DSP 内核的数据存储器。

该解决方案是一个高度可扩展的平台,内核数量以及 硬连线单元的尺寸取决于有针对性的配置。CEVA-XC 可以 高频率运行,并且大多数配置都可以由一个独特的内核处 理,同时还释放大部分的内核处理能力。客户可以利用这些 多余的处理能力进行分化、扩展或增强。

对于最大配置,例如 8x8,使用两个 CEVA-XC 内核共

享关键元件的处理负荷,从而实现架构缩放。与前导字段和 数据字段的频率域处理相对应,分离很容易实现:每个内核 处理子载波的一半即可。负责 FFT/IFFT 处理的时间频率单 元将已处理子载波总数的一半发送到每个核心或从其接收。

4 硬件加速器

本节介绍了不同的硬连线单元,重点说明了它们如何 作为配置的功能进行缩放。

4.1 无线接口单元

遵照 IEEE 802.11 规范,无线局域网为多设备网络使用 CSMA/CA(防冲突载波侦听机制)机制。每个设备都应该 侦听频道,并在自己尝试传输之前确认没有正在进行的传 输。因为它不能“预先”知道下一个感兴趣帧的到达时间, 所以默认情况下 Wi-Fi 系统侦听介质,根据标准要求生成空 闲频道检测 (CCA) 指示并检测感兴趣的信号(它必须为这 些信号合理设置射频和大约 4us 的模拟增益)。这些极度依 赖时间的操作完全由 RIU 处理。

RIU 的核心是一个微编码状态机,它控制高度可配置的处理块。这种上层的可编程性大大简化了对特定射频实现的 适配(特定增益级将在 LNA、下变频混频器和 VGA之间进 行划分 )的过程,并允许在硅上精细优化。

在数据路径上,前端单元负责固定的DAC/ADC 采样速 率和与帧带宽的功能成比例的频域处理速率之间的 Tx/Rx 数字上采样/下采样。它还负责来自/到达主信道的频率偏移。在 80MHz 信道操作模式下,固定的 ADC/DAC 采样速率为160MHz,并且只需要 Tx/Rx 20/40/80 滤波器块。如果支持160MHz 信道操作模式,将会添加 Tx/Rx 160 滤波器以适应320MHz ADC/DAC 使用的频率。还可以轻松定制 DAC 接口 以适应更高的采样速率,从而满足特定的无线电要求。

RIU 包含与天线相同数量的前端单元。RIU 还可以选择包含直接连接到 MAC PHY IF 的完整DSSS/CCK 调制解调器,并且不产生 DSP 开销。

4.2 时间频率单元

时间频率单元 (TFU) 主要提供减轻 DSP 负荷所需的

FFT/IFFT 功能。

在接收前导数据时,TFU 只是简单地将数据从 RIU 传 送到 DSP, 这会执行所有的同步估计。 在 TFU 接收根据 DSP 估计的 OFDM 符号边界后,它可以在 OFDM 符号序列 中同步自己,并向 DSP 提供 FFT 输出。

在 80MHz 信道操作模式下,FFT 的大小在 64 点、128 点和 256 点之间变化,与所用帧带宽的功能成比例。如果 支持 160MHz 信道操作模式,将需要一个可以根据 256 点 FFT/IFFT 计算 512 点 FFT/IFFT 的附加块。

在 Rx 数据路径上,TFU 还可以在 FFT 前执行时域 DC

和频率偏移补偿,待补偿的偏移值由 DSP 提供。

4.3 位处理单元

位处理单元 (BPU) 执行多个位域运算,特别是:? 在接收模式下, 它执行部分去交错、 流多路复用、 卷积解码和一些解扰运算。

? 在发送模式下,它执行加扰、卷积编码、流解复用和一些交错运算。

要求最苛刻的处理是卷积解码,它由多个软输入维特 比解码器并行处理。按照标准的定义,维特比解码器的数量 取决于数据传输速率。

4.4 平滑滤波单元

平滑滤波单元 (SMU) 对频域中的信道估计进行滤波, 以减少估计噪声,而这些噪声会影响从前导数据获取的信道 系数估计。所以它可以显著提高系统的灵敏度。

在 MIMO 操作中,信道矩阵的每个系数单独滤波(虽

然他们可以并行滤波)。SMU 中实例化的滤波器数量取决 于延迟要求。在需要多个内核并行运行的配置中,SMU 的 数量与内核的数量相同。

4.5 QR 分解单元

QR 分解单元 (QRU) 可帮助执行其复杂度对应一个关键路径的均衡器计算。但由于它的通用性,它也参与许多其

他处理任务,包括支持波束成形所需的信道估计的 SVD 实现。它也被用于预编码矩阵的复杂计算,作为 MU-MIMO AP 来处理 MU-MIMO 传输。

对于 SMU,实例化组件的数量取决于延迟要求,QRU

的数量与内核的数量相同。

4.6 MAC-PHY 接口单元

MacPhy 接口单元 (MPU) 负责 MAC 接口并执行多项运 算:

? 在接收模式下,它从 SIG 字段准备 Rx-Vector 并将其

提供给 MAC。它还处理 MacPhy IF 并将数据从调制解调器发 送到 MAC。

? 在发送模式下,它对来自 MAC 的 Tx-Vector 进行解 码,并将包含的信息提供给调制解调器。它准备 SIG 符号的 内容,处理 MacPhy IF 并从 MAC 发送数据到调制解调器。

(未完待续)

802 11ac Wave 3 解调器 20170203 相关文章:

- 无线升级到802.11n 应考虑的因素有哪些?(10-30)

- 解读802.11y:下一代Wi-Fi干扰避免机制(01-03)

- 802.11n对WLAN安全的影响(05-30)

- lEEE802.16标准及WiMAX发展情况介绍(03-06)

- 全新第5代WiFi 802.11ac无线标准概述(03-29)

- IXIA引入第五代WI-FI标准测试新解决方案(05-27)