基于SOPC技术的异步串行通信IP核的设计与实现

摘要:介绍了SoPC(System on a Programmable Chip)系统的概念和特点,给出了基于PLB总线的异步串行通信(UART)IP核的硬件设计和实现。通过将设计好的UART IP核集成到SoPC系统中加以验证,证明了所设计的UARTIP核可以正常工作。该设计方案为其他基于SoPC系统IP核的开发提供了一定的参考。

关键词:SoPC;UKRT;PLB;IPIF;FPGA

随着嵌入式技术的发展,基于SoPC技术的嵌入式系统所具有的软硬件可裁减、可扩充、可升级以及可在线修改的特点越来越受到人们的重视。SoPC系统通常具有以下基本特征:采用大容量可编程逻辑器件来实现,单芯片、低功耗;至少包含1个以上的嵌入式处理器IP核;具有一个或多条片上总线作为系统扩展功能的接口;具有充足的片上可编程逻辑资源,用户可以根据需要扩充功能部件。

异步串行通信协议(UART)以低成本、高可靠性等优点而广泛应用于嵌入式系统中,多篇文献也讨论了UART协议的硬件设计方法,但多数只限于讨论UART协议的硬件实现,缺少从SoPC系统的角度论述UART IP核的设计方法。本文以UART IP核和PLB总线为例,讨论了在SoPC系统下UART IP核的设计方法,该方法对其他IP核的设计有一定的参考作用。

1 UART协议介绍

UART是一种串行异步通信方式,它采用RS232电平在串行链路上进行全双工的通信,其数据传输格式如图1所示:UART协议在空闲时为高电平,通过发送起始位提示接收方数据传输即将开始,接着传输8位有效数据位和奇偶检验位,最后发送停止位表示一个字符传输完成。

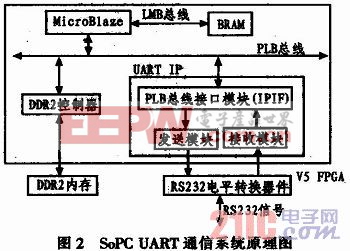

本文设计的SOPC UART通信系统主要包括MicroBlaze处理器、PLB总线、UART IP核和DDR2控制器IP核,如图2所示。

MicroBlaze处理器是Xilinx公司针对其FPGA器件优化的32位微处理器核,它采用RISC(Reduced Instruction System Computer)架构和哈佛总线结构,具有独立32位数据和指令总线,能够高速执行和访问片上存储器和片外存储器上的程序与数据;提供本地块存储器总线(LMB)、处理器本地总线(PLB)等总线接口。

PLB总线作为IBM CoreConnect总线协议簇中的一部分,广泛的应用于IBM PowerPC处理器架构中。该总线具有总线地址空间大,总线吞吐率高,能支持多个主从设备连接等特点。如图3所示,MicroBlaze处理器通过PLB总线与UARTIP核、DDR2控制器相互连接,各部件之间通过PLB总线协议进行交互。其中,MicroBlaze处理器作为主设备完成系统控制和UART通信流程控制,UART IP核作为从设备在主设备的控制下完成异步串行通信,DDR2存储指令和数据。

MicroBlaze处理器和DDR2控制器采用Xilinx公司提供的IP核,UART IP核由用户编写逻辑,它是文中设计的主要内容,对此模块的设计将在下一节进行详细阐述。

3 UART IP核设计

3.1 PLB Slave Single模块介绍

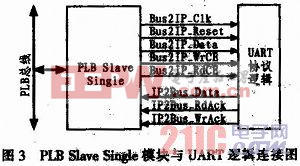

如上,UABT IP核作为PLB总线的从设备,必须提供PLB总线接口。但由于PLB总线协议复杂,实现其接口难度较大,Xilinx公司为了使用户编写的逻辑能够方便的连结到PLB总线上,提供了一种PLB总线与用户逻辑之间的接口模块(IPIF,IP Interface),利用它简化了PLB总线接口信号、总线协议和其他接口相关问题。IPIF接口逻辑中最简单的模块称为PLB Slave Single模块,它提供了一种轻量级的PLB总线接口,为PLB总线主设备提供了解析从设备地址空间,读写从设备寄存器/存储空间等基本服务。本文设计的UARTIP核与MicroBlaze处理器之间仅通过寄存器的读写进行交互,PLB Slave Single模块很好的满足了该设计要求,因此采用PLB Slave Single模块与UART逻辑共同构成了UART IP核。PLB Slave Single模块与UART逻辑之间的连接关系如图3所示,接口信号说明如表1所示。

在系统中,UART IP核的内部寄存器组映射为处理器的某段地址空间,MicroBlaze处理器通过对该段地址的读写实现对UART IP核的访问。当MicroBlaze处理器访问UART IP核的某个寄存器时,PLB总线会产生相应的地址信号和读写信号,该信号被UART IP核中的PLB Slave Single模块解析并生成相应的IPIF信号,UART IP核中的UABT逻辑响应该IPIF信号,完成寄存器的读写。

3.2 UART IP核寄存器组设计

文中设计的UART IP核提供了5个寄存器,如表2所示。其中发送寄存器和读接收寄存器完成UART数据的发送和接收。状态寄存器提供了UART IP核内部状态,包括接收数据有效,发送FIFO满,接收FIFO满,奇偶校验错等状态。控制寄存器提供了UART IP核复位功能。配置寄存器提供了波特率设置,奇偶校验位设置等功能。

3. 3 UART协议逻辑模块设计

本文设计的UART协议逻辑模块主要包括波特率产生模块,发送模块,接收模块,寄存器组等几个部分,其结构如图4所示。寄存器组说明如表2,其他几个模块的设计如图4所示。

IP 设计 实现 通信 串行 SOPC 技术 异步 基于 相关文章:

- WLAN与VoIP技术结合促进企业通信发展(02-11)

- IP微波:现代应急通信的新利器(12-15)

- IP微波助力光网成环(05-18)

- iPhone代替信用卡Visa推出配件In2Pay(05-19)

- 狂人设计之iPhone 4(07-05)

- 未来iPhone:手上投影 (10-25)