基于DDC和DUC的大带宽DRFM设计与实现

x4(n)、x5(n)、x6(n)、x7(n)。由式(3)可知,x(n)的偶数项对应其同相分量I路信号,奇数项对应其正交分量Q路信号。于是,对以上的8路信号进行处理,得到4路并行的I路信号xI0、xI1、xI2、xI3和4路并行的Q路信号xQ0、xQ1、xQ2、xQ3,其中xI0=x0(n)、xI1=x2(n)、xI2=x4(n)、xI3=x6(n)、xQ0=x1(n)、xQ1=x3(n)、xQ2=x5(n)、xQ3=x7(n)。将得到的4路并行的I路信号与4路并行的Q路信号分别通过满足式(5)的时延滤波器,使得I路信号和Q路信号在时域上对齐。经过时延滤波器后,得到I路4路并行信号xII0(n)、xII1(n)、xII2(n)、xII3(n),和Q路4路并行信号xQQ0(n)、xQQ1(n)、xQQ2(n)、xQQ3(n)。

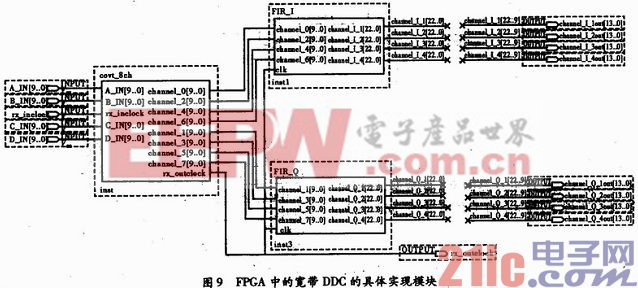

虽然信号x(n)经过抽取后变成了8路信号,经过DDC后变成了4路并行的I路和Q路信号,尽管每一路保存的I、Q两路信号对应的复信号与原信号相比,都有一定的频谱损失,但这4路并行的信号总体却完整保存了信号x(n)的频谱和相位信息。若要恢复信号x(n),只需经过一个相反过程即可。该宽带DDC的多相滤波结构在FPGA中具体实现的模块如图9所示。

图9中第1模块实现将信号x(n)抽取变为8路信号,分离出I路和Q路数据。第2,3模块实现的是将并行4路的I路和Q路数据经过各自对应的滤波器实现时域上的对齐,并最终将中频数字信号变成基带信号。

3.2 FPGA中Doppler模块的实现

多普勒调制原理

,还原I、Q两路在时域上的非对齐性,然后各自完成4倍的内插,实现数字上变频,其结构如图12所示。

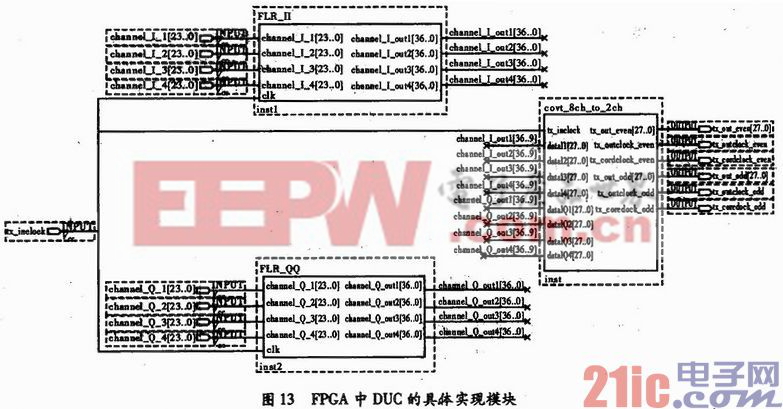

该数字上变频在FPGA中的具体实现模块如图13所示。

3.4 系统在Modelsim中的仿真

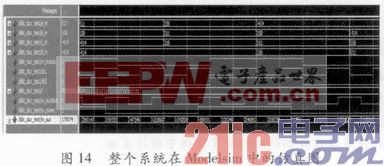

将FPGA中的整个系统在Modelsim中进行仿真,结果如图14所示。

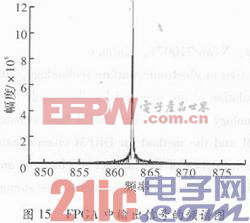

将图14得到的输出信号的离散的值导入到Matlab中,查看其频谱图,如图15所示。

如图15所示,输出信号频率为862.5 MHz,与图5仿真结果相同,由此得出,在FPGA中的整个DRFM系统实现的功能与理论上得到的结果一致,从而完成了DRFM系统的功能,达到了预期的效果。

4 结束语

随着超宽带高分辨率雷达在未来战场发挥的作用越来越大,对于超带宽雷达的干扰技术研究,将成为雷达对抗领域的重要研究方向。文中针对基于现代化软件无线电原理的数字下变频(DDC)和数字上变频(DUC)技术,对实现的DRFM系统进行了分析及系统仿真,得出的结论与预想结果吻合良好,证明了系统的可行性。

设计 实现 DRFM 带宽 DDC DUC 基于 相关文章:

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)

- 无线通信网络设计与现场测试(10-10)

- WiMAX数据传输加密方案设计与实现(05-25)

- 高性能TD-SCDMA接收机的设计(03-15)

- 初步设计WiMAX射频系统(03-29)