基于CPCI接口的SpaceWire总线通讯模块设计

引言

随着航天技术的进步和卫星与高空探测技术的发展, 需要一种高速、可扩展、低功耗、低成本的通用通讯链路接口来满足星载高速数据传输要求。SpaceWire 总线标准就是一种高速的、点对点、全双工的串行总线网络, 以IEEE1355-1995和LVDS 两个商业标准相结合而提出的一种星载数据总线。本文在研究SpaceWire 总线协议的基础上,分析了基于CPCI接口的SpaceWire节点通讯板卡的硬件实现架构,并着重分析CPCI接口电路电源管理功能、PCI桥接电路以及上位机软件驱动的生成原理。

1 SpaceWire概述

SpaceWire 是为更好地满足星载设备间高速数据传输需求而提出一种高速的(2Mbit/s至400Mbit/s,目前实现的宇航级节点设备之间的速度为200Mbit/s)、点对点、全双工的串行总线网络,在2003年1月正式成为欧空局标准。它的提出主要致力于航天器内有效载荷系统数据和控制信息的处理, 以满足未来高性能高速数据传输为目标, 提供了一种统一的用来连接传感器、数据处理单元、大容量存储器、遥测子系统以及电地支持设备EGSE ( electronic ground support equipment ) 的基础架构。

SpaceWire 标准具体包括了链路、节点和路由三方面的内容。本文着重讨论节点的功能,所谓SpaceWire 节点, 是指传输包的流出设备或者流向设备, 可以是处理器、存储单元、传感器、电地支持设备( EGSE ) 或连接在SpaceWire总线网络上的其它单元。

2 SpaceWire节点通讯板卡硬件设计

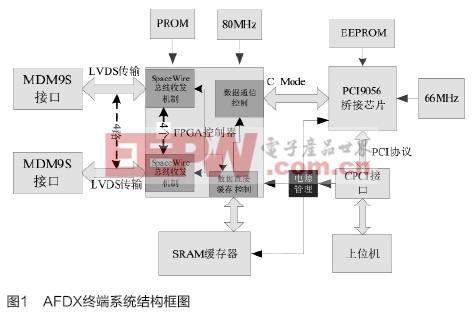

EMBC1000-CPCISPW是欧比特公司自主研制的完全遵循并实现ECSS-E-ST-50-12C协议规范的航天设备间的高速SpaceWire数据总线的,支持热插拔的CPCI接口的节点终端通讯板卡(本板卡实现了200Mbit/s的速率)。此SpaceWire总线节点通讯板卡可以嵌入在航天子系统中,将航天子系统中与其它SpaceWire网络之间连接,保证航天子系统之间高速、实时、确定、可靠地进行数据交换。硬件架构如图l所示,分为FPGA控制模块、CPCI接口电源管理模块、MDM9S接口模块和SRAM缓存模块。各模块的功能如下:

FPGA控制模块:FPGA采用Altera公司的EP3C55F484I7N芯片,时钟频率采用80MHz,同时为了实现SpaceWire总线传输速率,FPGA内部采用了PLL对时钟进行了分频,实现4路SpaceWire总线通信协议接口功能,硬件实现LVDS信号传输,实现数据通讯过程中产生的大量数据实现缓存并与PCI9056通信接口等功能;

SRAM缓存器:4M字节的SRAM用于实现存储SPW总线收发机制中产生的大容量高速数据的缓存功能;

MDM9S接口模块:MDM9S接口实现FPGA的LVDS信号与外部SPW设备之间的接口功能;

PCI接口模块:实现PCI总线的接口协议功能,通过CPCI接口实现FPGA与上位机软件间进行数据的通信,同时实现支持热插拔的板卡的电源管理功能;

电源管理模块:与PCI9056芯片以及CPCI接口共同完成设备的电源热插拔功能。

3 CPCI接口电源电路分析

PCI设备的热插拔功能主要用于具备CPCI接口的装置,热插拔功能允许板卡随意从设备中插拔而不影响装置操作系统的正常运行。电源芯片电路如图2所示,LTC1643L是一个允许CPCI型设备进行安全插入和拔出的电源管理控制器,将系统的CPCI插槽电源接入到SpaceWire板卡,图中IRF7413是一个N型MOS管,用于控制3.3V和5V的电源通断供应,而-12V和+12V电源由片上开关供应,所有的电压的上升时间可以达到一个可编程的速率,同时该芯片还具备电源过流故障时的短路保护。

PCI9056的引脚BD_SEL#是CPCI接口中最小的插针之一,BD_SEL#连接LTC1643L的使能引脚,低电平时有效开启LTC1643L工作并同时给板卡供电。R10是一个0.018欧姆,0.5W,精度为1%的精密电阻,用于过流保护的电压检测电阻。当板卡发生故障导致电流超过额定值之后,R10两端的压差将增大,SENSE引脚将此过流信息反馈至LTC1643L电源管理器,同时切断电源供应,起到电源过流保护的功能。

4 PCI桥接电路分析

在SpaceWire总线节点终端系统与航电计算机系统之间实现PCI通讯大致有两个方式,其一就是采用可编程器件作为一个独立的模块实现PCI协议,另一种方式就是采用专用PCI协议芯片。本系统的设计出于性能稳定性和结构简易性方面的考虑,选择用PLX公司生产的PCI9056集成芯片,该芯片可以设置成多种传输模式,完成SpaceWire总线节点与航电设备之间的通信桥接功能。

在PCI9056与本地FPGA之间的通信分为直接主模式(Direct Master Mode)、直接从模式(Direct Slave Mode)和DMA模式。由于PCI通信要求达到SpaceWire总线网络的2Mbit/s至400Mbit/s通讯速率(本板卡实现了200Mbit/s),这里采用的芯片时钟频率为66MHz,传输模式为

SpaceWire IEEE1355-1995 LVDS CPCI PCI9056 201406 相关文章:

- 千兆采样ADC确保直接RF变频(05-01)

- 隔离式LVDS接口电路(11-07)

- 基于LVDS高速串行总线技术的传输方案(06-07)

- 基于FPGA的LVDS高速数据通信卡设计(05-23)

- 采用LpLVDS和CTL实现便携式产品中的接口设计(06-08)

- 采用LVDS高速串行总线技术的传输方案(08-30)