基于CPLD的异步ASI/SDI信号电复接光传输设备设计

: std_logic;

signal N_17 : std_logic;

signal N_21 : std_logic;

signal N_22 : std_logic;

signal N_23 : std_logic;

signal N_24 : std_logic;

begin

I30 : G_D Port Map ( CLK=>N_25, D=>N_13, Q=>N_22 );

I29 : G_D Port Map ( CLK=>N_25, D=>N_16, Q=>N_23 );

I34 : G_OUTPUT Port Map ( I=>N_22, O=>Q0 );

I33 : G_OUTPUT Port Map ( I=>N_23, O=>Q1 );

I2 : G_INPUT Port Map ( I=>CLK, O=>N_25 );

I7 : G_INPUT Port Map ( I=>A, O=>N_12 );

I8 : G_INPUT Port Map ( I=>LD, O=>N_21 );

I6 : G_INPUT Port Map ( I=>B, O=>N_15 );

I12 : G_2OR Port Map ( A=>N_17, B=>N_24, Y=>N_16 );

I16 : G_2AND1 Port Map ( AN=>N_21, B=>N_22, Y=>N_24 );

I21 : G_2AND Port Map ( A=>N_21, B=>N_12, Y=>N_13 );

I20 : G_2AND Port Map ( A=>N_21, B=>N_15, Y=>N_17 );

end SCHEMATIC;

architecture SCHEMATIC of 2BS-P is

SIGNAL gnd : std_logic := '0';

SIGNAL vcc : std_logic := '1';

signal N_5 : std_logic;

signal N_1 : std_logic;

signal N_3 : std_logic;

signal N_4 : std_logic;

begin

I8 : G_OUTPUT Port Map ( I=>N_4, O=>Q0 );

I1 : G_OUTPUT Port Map ( I=>N_5, O=>Q1 );

I2 : G_INPUT Port Map ( I=>CLK, O=>N_3 );

I3 : G_INPUT Port Map ( I=>SIN, O=>N_1 );

I7 : G_D Port Map ( CLK=>N_3, D=>N_4, Q=>N_5 );

I4 : G_D Port Map ( CLK=>N_3, D=>N_1, Q=>N_4 );

end SCHEMATIC;

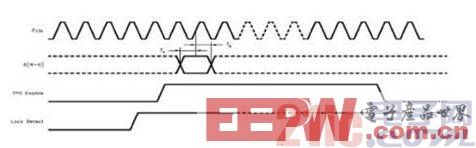

编码部分电路处理过程如图8所示。收端光模块收到数据后,通过CPLD的解复接程序恢复出并行数据和同步时钟,再通过编码芯片电路恢复出原始的高速串行信号,经过电缆驱动芯片驱动后最终由传输设备输出,完成整个传输过程。其中,编码电路部分的信号时序如图9所示。

图8 编码部分电路处理过程

图9 编码电路信号时序图

结束语

基于CPLD的异步ASI/SDI信号电复接光传输设备的设计使用了最新的ASI/SDI信号电复接/分接技术,可以实现两路信号的时分复用传输,替代了以往以波分复用技术为基础的多路异步信号传输模式,大大节省了生产成本,使产品的市场竞争力进一步提高。

- 采用CPLD电器定时开关控制系统电路(04-08)

- 基于CPLD的单片机与ISA总线接口的并行通信设计(06-19)

- 基于CPLD的OMA-L137与ADS1178数据通信设计方案(09-11)

- 单片机脉冲信号源的CPLD实现方案(05-18)

- CPLD的串口通信设计(04-30)

- GigaSite:开创移动宽带新未来(12-05)