基于FPGA的MIMO视频缓存器的设计与实现

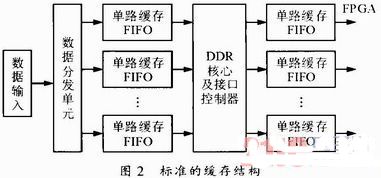

IFO,结构如图2所示。

这种结构的优点在于,对每一路节目,都有单独的缓存空间对其进行缓存,各路节目相对独立,互不干扰;在节目路数较少的情况下,该结构效率较高,便于扩展。

但上述结构存在的问题在于,如果节目路数过多,输入数据流量过大,会导致FPGA内部缓存数量成几何上升,极大的消耗FPGA资源,降低运行时钟频率,造成系统综合后速度下降。

4.2 端口固定的MIMO结构缓存器

由于标准的MIMO结构存在的问题,难以达到本文所需的应用要求,因此存这里提出的一种改进型设计。这种设计不像标准的MIMO那样对DDR进行逻辑结构上的缓存,而是通过固定DDR高位地址,采用物理结构缓存的方式进行快速存储,如图3所示。

在这种结构中,外部流处理模块先将数据流与该数据流存储的通道号分发至缓存RAM和地址转换模块,再由调度模块调度转换后的对应地址指针,将其发送到DDR上对应的物理存储空间而在输出端口也以同样的方式只针对物理输出端口,这就要求有一个读请求队列,以便将要读的目的通道提前发送。在这里调度模块能够实时检测各个通道使用情况,并将数据流快速分发。这种结构对于EQAM这种一个物理IP端口输入几百路流的设备,可以极大地降低FPGA内部RAM的消耗,且对DDR影响也较小,不会过多降低系统性能。而且在前端数据缓存中直接使用RAM而不使用FIFO更有利于同步数据流和对应地址。

5 系统测试

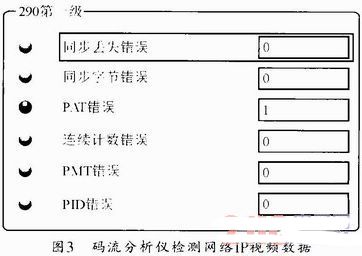

为了测试本设计止确性,将上述模块嵌入EQAM系统后,接收来至网络的IP视频数据,通过码流分析仪检测数据结果后发现,经DDR缓存后数据流包计数器没有错误,没有出现丢包情况,码流分析仪自带播放器能够清晰连续播放节日,如图3所示。但在节目转换过程中由于节目不同会产生PAT错误,该错误不影响节目正常播放。

6 结束语

本文在这里提出了一种改进MIMO结构DDR缓存器,并对核心控制模块实现功能进行了描述,讨论了改进后的设计对系统的影响。最终测试结果也表明,本设计完全可以应用于多通道大容量的视频设备的缓存中。

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)