高速信号、时钟及数据捕捉

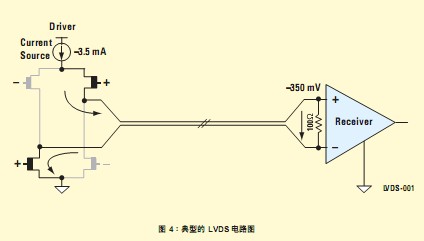

并非只利用一个 8 位总线,按照取样率的速度传送数据。若采用这个方法,数据传输率会减慢一半速度,但数据的位数则会增加。以 1GSPS 的取样率为例,模/数转换器能以 500MHz 的速率输出已转换的数据。即使速度如此低,大部分离散式或内置的 FPGA 存储器仍然很难保证满足要求。因此,较为理想的方法是采用双倍数据传输率 (DDR) 技术,利用时钟的上升及下降边缘将数据传送至输出端。此外,若利用 DDR 技术传送数据,速度保持不变,而时钟频率则会减慢一半至 250MHz。这是较为容易控制的频率,而且属于 CMOS 存储器电路的操作频率范围内。有关数据必须先在 FPGA 的输入端加上对中间数据锁存,才可存入存储器之内。第一个锁存必须利用同相位的数据时钟定时,而第二个锁存则必须利用 180 异相的信号或反向数据时钟定时 (参看图5)。 图 3 取样率为 1 GSPS 时的 489MHz 正弦波 FFT 波动图 图4 典型的 LVDS 电路图 图5 FPGA 数据捕捉结构 为了简化这个定时上的规定,FPGA 都设有数字时钟管理电路。基本上,这些时钟管理电路都属于锁相环路 (PPL) 或延迟锁定环路 (DLL),其优点是可以容许由内部产生时钟信号,并确保所有时钟信号的相位都按照输入时钟锁定,其分接头的相位延迟分别为 0、90、180 及 270。这种时钟管理技术的优点是可以提供准确的 180 位移时钟,使 DDR 定时电路可以顺畅地执行其正常功能,以便 FPGA 存储器可以捕捉与下降边缘同步的输入信号,然后利用数据闩锁将输入数据妥善保存。锁定后的输入数据可以再传送往先进先出存储器或数据块 RAM,以便系统微控制器可以轻易以远比先前慢的速度检索有关数据,然后才作进一步的处理。 结语 系统设计工程师若要设计一个完善的超高速数据转换系统,需要面对很多挑战。这类转换系统是真真正正的混合信号系统,我们必须小心考量所有子电路的优缺点,才可确保模/数转换器能够充分发挥其强劲性能。工程师只要采用现成的元件,便能以极低的成本组建符合低抖动要求的定时系统。此外,目前市场上提供的 FPGA 芯片都可为必须全面符合 LVDS 规定而又需要加设时钟管理电路的系统提供支持。■

- 让LM1875声音更靓(02-07)

- 现代通信系统电源设计(02-13)

- 便携式应用处理器设计中的电源管理(03-02)

- 采用开关电容器电路的高效白光LED驱动方案(05-07)

- 通用电源设计指南(05-22)

- 开关电源设计:PWM电流模式双重同步降压转换器LM5642(05-18)