DM642开发与应用

视频实时处理,由于视频处理中数据量大,要求速度快因此采用TM320DM642。视频处理机应用于视频采集、视频处理、视频输出的视频实时处理。视频处理机的解决方案有多种选择,但是市场主流产品一般选择两种方案:1)采用CPU+ASIC。2)采用双CPU结构,即一个嵌入式CPU和一个专用信号处理芯片DSP。受专用DSP芯片处理能力的限制,现有的嵌入式中使视频处理机的视频处理算法基本是H.263以下的标准。

l 硬件设计

本文介绍一种基于TMS320DM642 DSP的视频采集设计方案。其操作系统、通信协议、网络协议、音视频处理软件均在一颗TMS320DM642上实现,降低了开发的难度。

TMS320DM642芯片简介:

TI公司的TMS320DM642(以下简称DM642)是一款专门面向多媒体应用的专用DSP。该DSP时钟高达600MHz,8个并行运算单元,处理能力达4800MIPS;采用二级缓存结构;具有64位外接存储器接口;兼容IEEE―1149.1(JTAG)边界扫描;为了面向多媒体应用,还集成了3个可配置的视频端口、面向音频应用的McASP(Multi Channel AudioSerial Pott)、10/100Mb/s的以太网MAC等外设。鉴于DM642的上述优点,本网系视频处理机统以DM642为核心,完成音视频信号的实时采集、压缩及传输功能。

系统电路组成如图1所示。从视频处理机的视频信号和从麦克风输入的音频信号经采集、A/D转换为数字信号后送入DSP。DSP在信源处对音视频信号进行压缩编码和合流,然后通过局域网或因特网将数据传输给视频监控中心。监控中心可同时监视多个现场,接收或发送报警信号,并根据需要通过异步串行总线RS-485实时控制,调整摄像头的方向和位置。

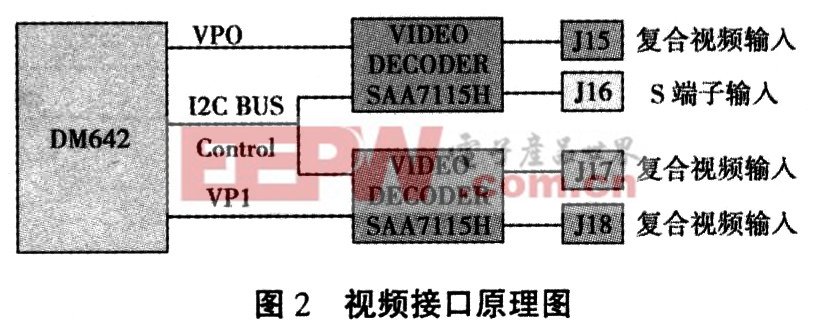

1.1 视频采集电路

本系统采用的视频解码芯片是Philips公司的SAA7115。从模拟视频输入口输入的全电视信号在SAA7115内部经过钳位、抗混叠滤波、A/D转换、YUV分离电路之后,在YUV到YCrCb的转换电路中转换成BT.656视频数据流,输入到压缩核心单元DM642中。DM642的3个视频口VP0、VP1、VP2与视频编解码芯片相接。在本系统中,只有一路视频输入,故VP1、VP2端口,VP0通道配置为8位BT.656视频输入口。视频数据的行/场同步信号包含在BT.656数字视频数据流的EAV(end ofactive video)和SAV(start of active video)时基信号中,视频口只需视频采样时钟和采样使能信号即可。SAA7115内部寄存器参数的配置和状态的读出通过I2C总线进行。视频接口的原理如图2所示。

1.2 视频编码电路

本系统采用的视频编码芯片是Philips公司的SAA7105H。DM642的视频口2用来驱动视频编码器,视频信号经过FPGA芯片,连到视频编码芯片PhilipsSAA7105H。FPGA用于扩展屏幕显示功能。视频输出信号支持RGB,高清晰度视频,PAL/NTSC复合视频和s端子视频信号。通过DM642的I2C总线对的内部寄存器编程实现不同输出。

1.3 音频输入/输出电路

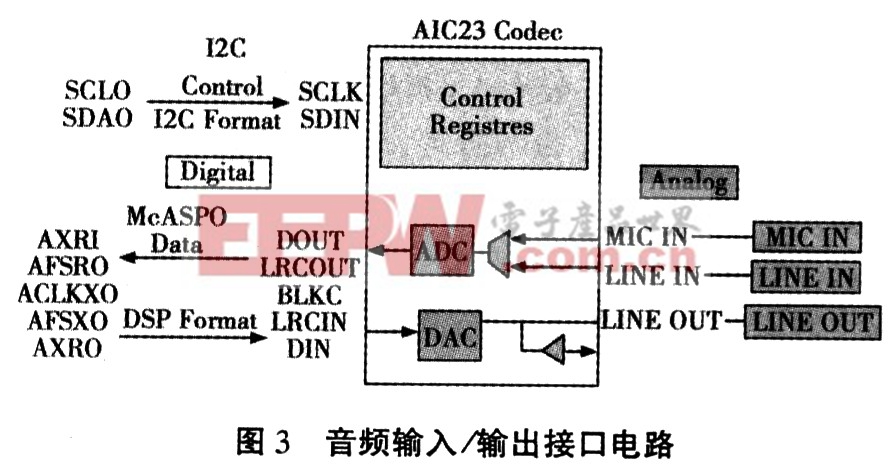

本系统采用TI的高性能立体声编解码器TLV320AIC23(以下简称AIC23)实现音频信号的采集和播放。AIC23与DM642的I/0电压兼容,可以实现与DM642的McASP接口无缝连接。在本系统中,AIC23工作于主模式,左右声道的采样字宽均为16bit。数据接口为DSP mode模式。通过I2C总线设置内部寄存器的工作参数和反馈状态信息。

因为网络传输的固有特点,音频数据和视频数据从网络摄像机端到达监控中心不可能是均匀的,如果网络摄像机端不做任何纠正处理,则很难保证音视频的同步输出。为了实现音频和视频的采样同步,本文利用锁相环PLLl708,从SAA7115的LLC引脚输出27MHz时钟,经PLLl708产生AIC23的主时钟MCLK。由于音视频采样信号采用同一个时钟源,就不会出现音视频不同步的问题。PLLl708的SCKO3引脚输出默认时钟频率18.433MHz,作为AIC23的输入主时钟MCLK。AIC23内部采用的时钟可通过设置寄存器由主时钟MCLK分频得到如图3。

1.4 以太网接口电路

本系统用LXT97l作为快速以太网物理层自适应收发器。由于LXT971支持IEEE 802.3标准,提供MII(mediaindependent interface)接口,可以支持MAC,而DM642内部正好集成有以太网媒体存取控制器,所以LXT971可以和DM642实现无缝连接。连接电路如图3所示,其中BHll02为l:1的隔离变压器。从DM642传输过来的数据通过LXT971转换为以太网物理层能接收的数据后,通过RJ一45头传输到因特网。

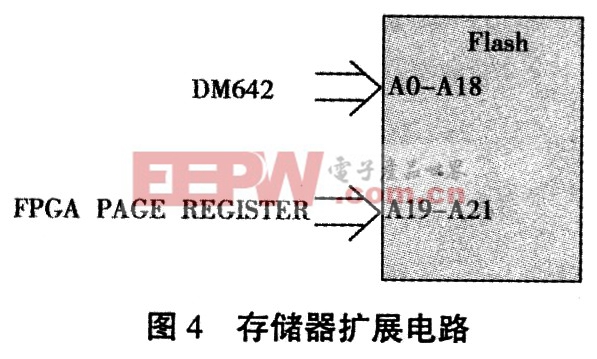

1.5 存储器扩展电路

DM642内部有16KB的一级程序缓存,16KB的一级数据缓存和256KB的程序数据共享二级缓存。但这对于直接处理图像数据是不够的,因此扩展了两片32MB的SDRAM来存放原始图像数据,4MB的FLASH来存放应用程序。二者都映射到DM642的外部数据空间。如图4。

1.6 FPGA电路

SPARTAN一3是XILINX公司生产的一种低工耗易开发应用。Spartan一3 FPGA具有两种类型的内存,可以满足不同的设计需求,即最大1.8Mb的真实双端口块RAM和最大520KB的分布式RAM,其封装形式为16位深×1位宽,可用作移位寄存器和FIFO。先进的时钟管理为高性能电路的设计者提供了更大的灵活性和更强的控制能力,最多四个数字时钟管理器(DCM),并带有9个外部输出;8个预设的全球时钟网络,即8根全局时钟线路和丰富的寻址。最多104个18×18乘法器,该乘法器模块允许两个18位二进制作为输入并计算输出36位结果,而专用的进位逻辑和高效级联,可实现更多功能。每秒最多3300亿次乘法和累加运算(MAC/s)、优秀的高速DSP功能的并行实现能力、灵活的串联架构,可实现成本砌能需求的最佳组合。

FPGA在视频处理机中完成屏幕显示功能,在默认模式下,DM642视频口2的数据可直接输出到视频编码芯片,在需要屏幕显示功能时,FPGA把内部FIFO中的数据和视频口输出得数据混和,对FPGA内部FIFO的访问可以通过对DM642的EMIF的CE3的地址空间的同步模式的访问实现。FPGA的同步存储器位于DM642的CE3地址空间,主要用于实现屏幕显示功能和粘和逻辑。

1.7 RS-485接口电路

该接口连接到摄像机的云台,用来控制云台的转动,调整摄像头的方向和位置。RS-485总线抗干扰能力强,能实现多站点远距离通信。本压缩卡拟采用UART芯片SCl6C550和MAXIM公司的MAX487E来实现RS-485信号的传输。SCl6C550主要功能是把DSP传送过来的并行信号转换为串行信号。SCl6C550内部的接收器和发送器各有16B的FIF0,能处理的串行信号的速率高达3Mbps。MAX487E是RS-485总线接口芯片,可以工作在全双工、半双工模式。传输速率可达2.5Mbps。

1.8 电源电路

整个压缩卡用一个5V的直流变压器供电。由这个5V的电压器产生1.4V和3.3V电压分别给DSP内核和I/O端口供电,产生另外一个3.3V给视频编解码及其他芯片供电。注意这两个3.3V电源要分开设计,以免电源噪声相互干扰。

由于DSP需要两种电压,所以要考虑供电系统的配合问题。加电过程中,应当保证内核电源先上电,最晚也应当与I/O电源一起加。关闭电源时,先关闭内核电源,再关闭I/O电源。讲究供电次序的原因在于:如果仅CPU内核获得供电,周边I/O没有供电,对芯片不会产生损害,只是没有输入/输出能力而已。如果反过来,周边I/O得到供电而CPU内核没有加电,那么芯片缓冲/马区动部分的晶体管将在一个未知状态下工作,这是非常危险的。

为了解决这个问题,本文采用了开关电源芯片TPS54310PWP,采用TPS54310PWP管脚SS/ENA接电容来使内核供电与I/O端口供电,这样,只有当1.4V电压有效之后,3.3V电压才开始上电,这就保证了DM642的内核电压先于I/O电压上电。

- UL1642锂电池安全标准(01-05)

- 开关电源设计:PWM电流模式双重同步降压转换器LM5642(05-18)

- 认识LED1642GW 完全可设置的智能16粒LED光源驱动器(04-12)

- 基于DM642的视音频采集器的设计(09-01)

- 基于DM642DSP的视频编码优化方法(09-01)

- 基于DM642的X.264编码器优化(10-26)