同步采样A/D转换器AD7262原理及应用

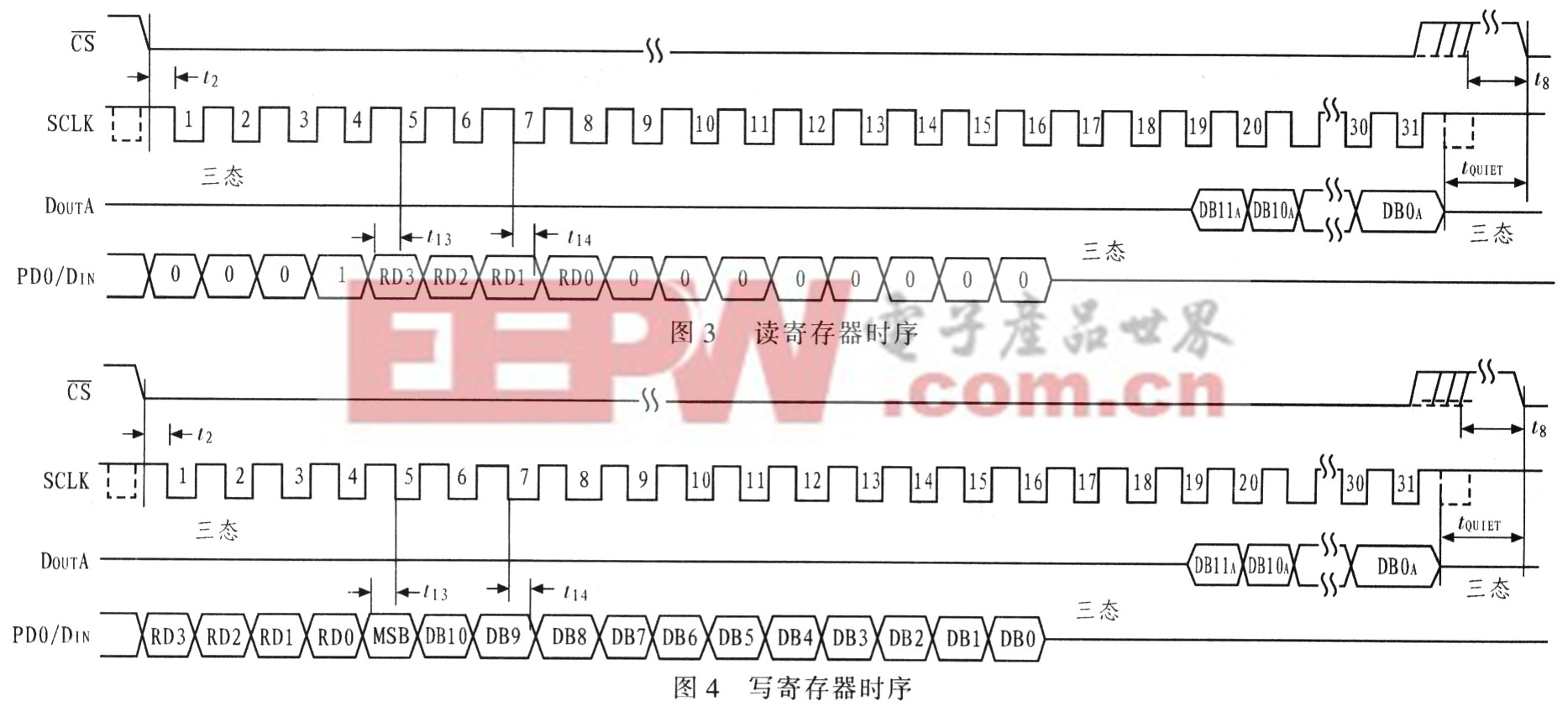

8向AD7262内部写入相关数据来实现各类动态配置。图3和图4为串行接口读写时序图。串行时钟SCLK提供转换时钟及AD7262转换后传输信息的控制。对于片内2个A/D转换器,AD7262有相应的2个输出引脚。数据从AD7262的DOUTA和DOUTB读龋用户可选用其中一个输出数据。

在CS下降沿,跟踪保持器处于保持模式。此时,采样、转

换同时被初始化模拟输入。这需要至少19个SCLK周期。第19个SCLK的下降沿到来时,AD7262恢复至跟踪模式,并设置DOUTA、DOUTB为使能。数据流由12位组成,MSB在前。转换结果MSB在SCLK第19个周期的下降沿由微控制器在第20个时钟SCLK的下降沿或上升沿读取。上升沿还是下降沿取决于所使用的SCLK的频率。如SCLK最大频率为40 MHz时,其读取数据时间是23 ns,则导致2 ns的建立时间。而这2 ns的建立时间无法与微控制器匹配。在这种情况下,就需要在时钟SCLK的上升沿开始读数据。这样,转换结果的MSB位在第19个SCLK下降沿,延迟15 ns,并在第20个周期SCLK的上升沿才被读出。依此类推,至第30个SCLK下降沿A/D转换器输出LSB,在第31个SCLK上升沿读出。反之,如果SCLK为32 MHz时,则下降沿读数据。在设计中SPI的通信时钟频率(LPC2378的P0.15)小于32 MHz,所以在时钟的下降沿由LPC2378读写数据。为提高系统的精度和稳定性,可加入一定阻值的耦合电容。

3.2 软件设计

AD7262内含6个寄存器,分别是A/D转换器的结果寄存器、控制寄存器、A/D转换器A和B的内部失调寄存器、A/D转换器A和B通道的外部增益寄存器。控制寄存器共有12位,其中,RD3~RD0是寄存器选择位。

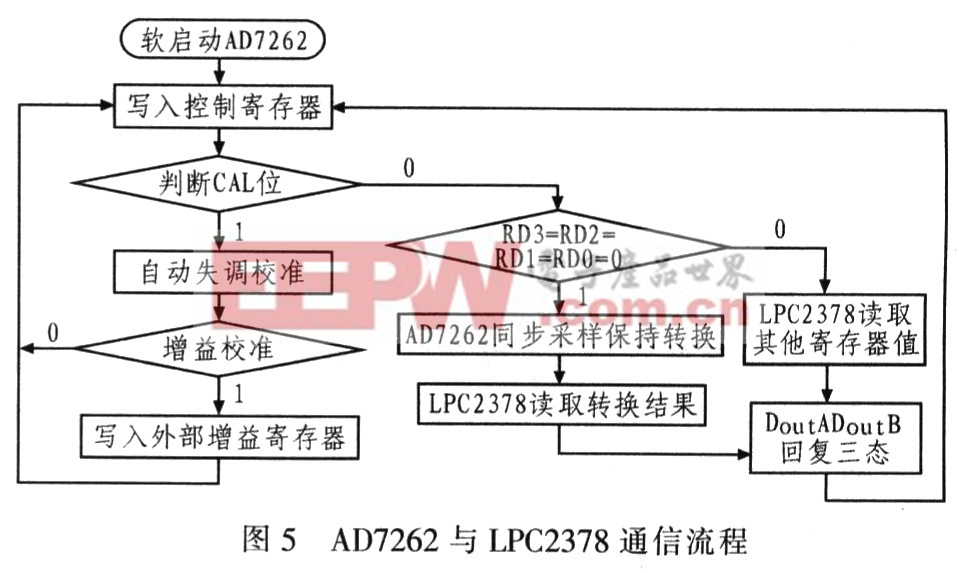

由于LPC2378和AD7262都兼容SPI接口,两者的编程只需按照时序图进行即可。此外LPC2378还有许多其他类型接口,所以便于实现网络化,详细流程参见图5。

软件设计中需要注意:CAL引脚在CS为低电平前必须至少保持2μs高电平以确保第一个转换周期中校准的准确性。如果在这段时间内,CAL出现低电平,将导致校准结果不准确。但如果继续为高电平,下一个校准转换则是准确的。另外在A/D转换过程中,CAL若出现高电平,转换结果也将不正确。AD7262的校准是在测量过程中,A/D转换前进行的。在测量过程中先校准再采样保持。与编程写寄存器,在时序上要分开。此外使用SPI接口,只有硬件复位是不够的,还要使用软件复位以保证读写数据的正确性。实际应用中,要将数字和模拟部分地线隔离。整个软件部分采用串口读写寄存器完成。

4 结束语

与其他A/D转换器相比,AD7262除了转换速度快、接口简单、低功耗、控制功能较强的特点外,还具有内嵌PGA、自动校准、同步采样等特点,适合于不同信号强度级别的多种电极传感器的信号检测、控制和电机控制系统。目前,该系统已成功应用于物理勘探电法实验仪器中,实现A-B和M-N的电极同步电压测量,效果较好。

- 同步采样转换器AD7262(08-25)

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 利用GM6801实现智能快速充电器设计(11-20)

- 稳定低噪声放大器中晶体管工作点的设计方法(下)(11-20)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)