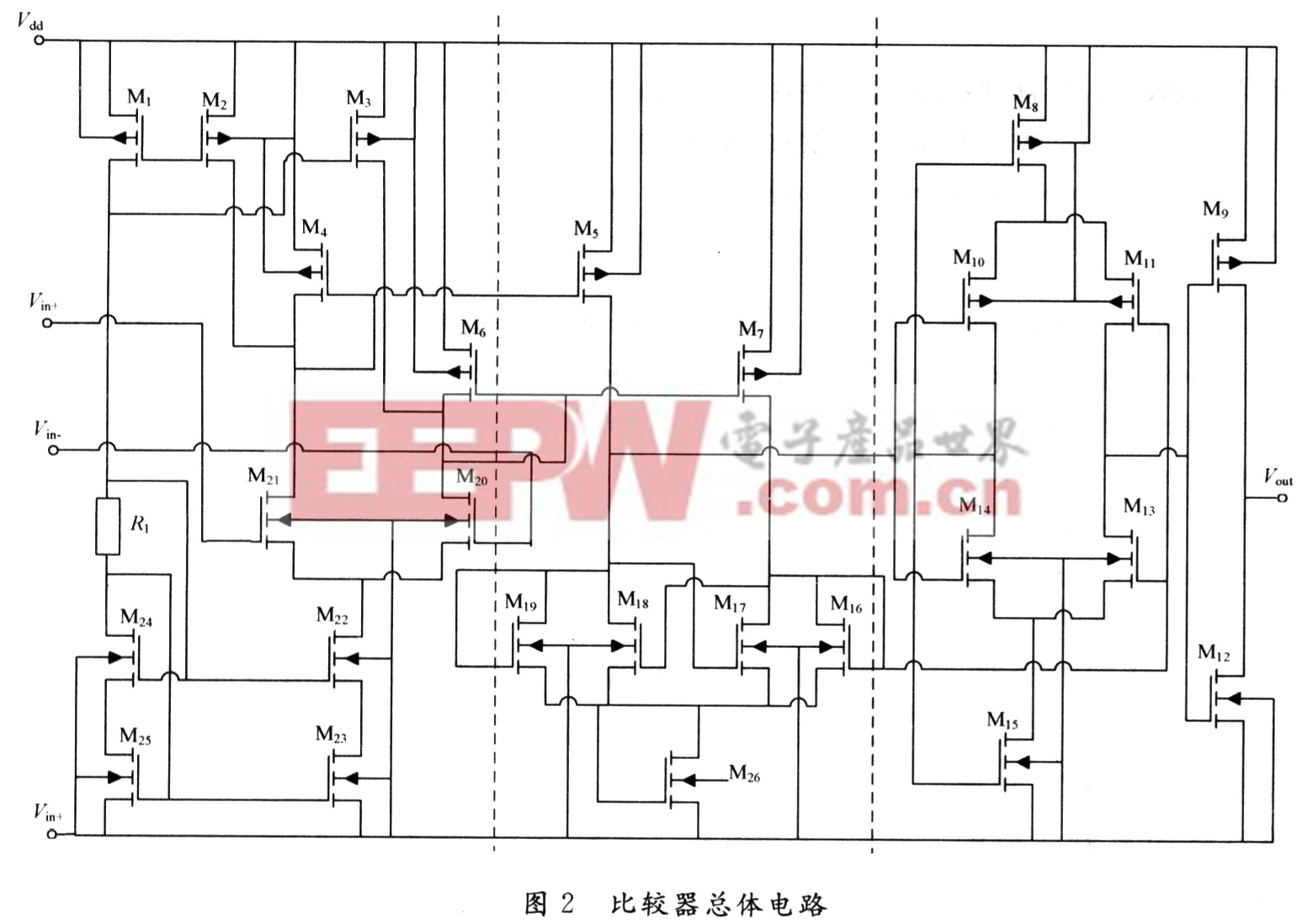

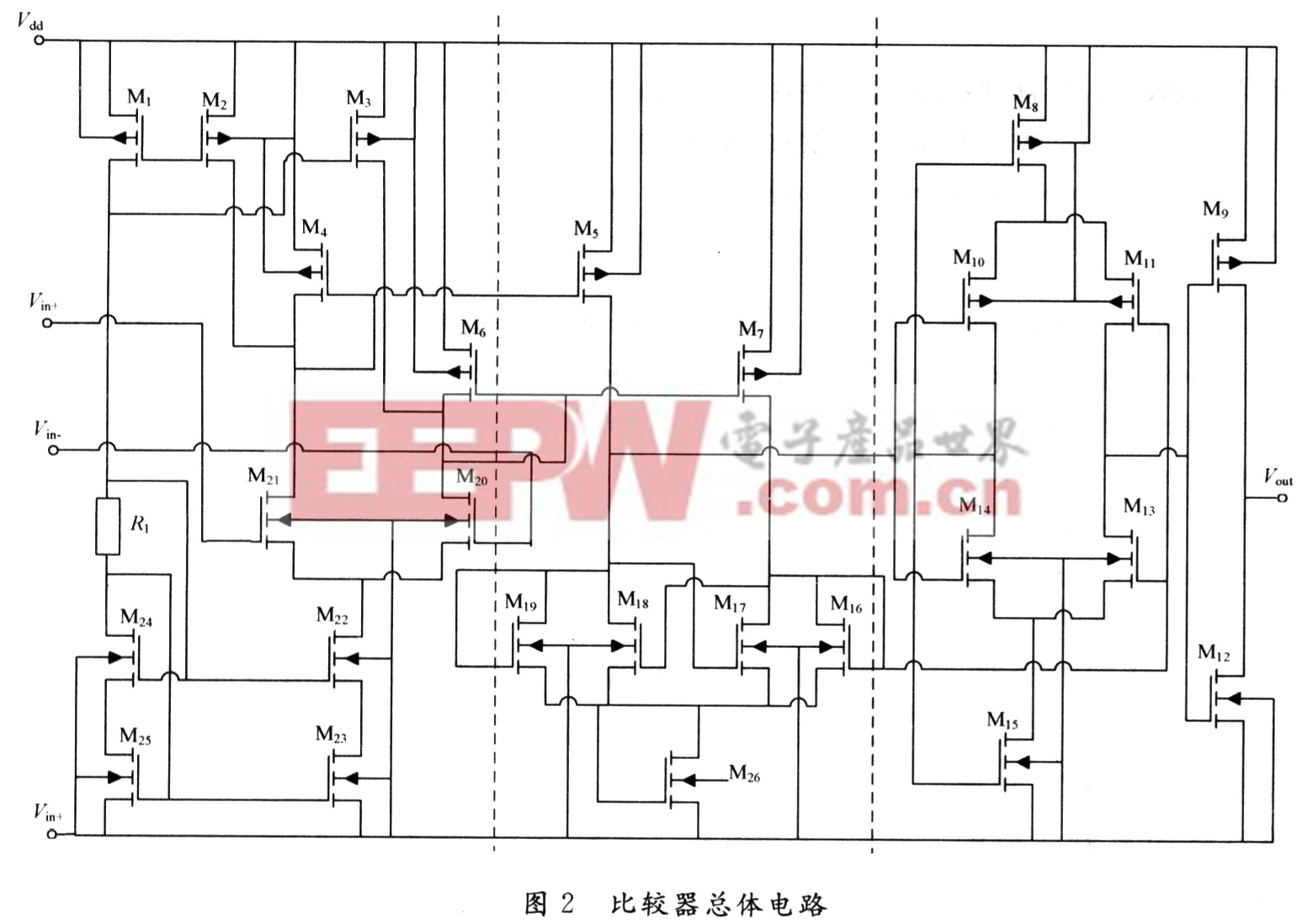

如图2中第一部分所示,M20和M21构成差分放大管;M4,M6组成有源负载。M2,M3分别与M4,M6并联,以向差分放大管注人大电流,同时也减小了M4和M6的宽长比,降低了电路的输入电容,以利于电路提高频率特性。该放大器的增益可表示为:

从式(1)可以看出,在管子宽长比确定后,Av与(1+ISD2/ISD4)1/2成正比,若M2向M21注入大电流,则在保证高频时能提高放大器的增益。该放大器的增益为12.9 dB(4.415 7倍),3 dB带宽为582.64 MHz。

1.2 锁存比较电路

锁存比较电路是整个比较器的核心部分,它应能区分毫伏量级的输入信号差。如图2中第二部分所示, M17,M18交叉互连实现正反馈,以提高比较电路的增益。利用前级预放大器的输出,控制锁存器输入电流I+,I_的变化,若I_远大于I_,则M16和 M18导通,Vout-△0,Uout+=(2L16I+/WμnCox)+VTHN;若I_增大而I+减小,M18的漏一源电压升高,当高到M17的 VTHN时,M17导通,此时M17管开始抽取原来流过M16管的电流,这会使M16管的漏一源电压下降,并导致M18管截止,电路的输出状态发生转换。当I-增大到一定程度时会导致M18进入饱和区,此时临界电流值I-=(I+)(W17μnCox/L17)/(W16μnCox/L16),该电流临界点也是输出电压发生转换的临界点。同理可得,当I+增大时,发生转换的电流临界点I+=(I-)(W17μnCox/L17)/ (W16μCox/L16)。

该锁存比较器发生转换时的输入电压差为1.37 mV。从锁存器的瞬态特性可以看出,在输入信号发生跳变时,通过比较输入信号和2.5 V参考信号,锁存比较器给出两个向相反方向变化的输出信号,实现了比较功能。

1.3 输出缓冲驱动级

输出缓冲驱动级(又称后放大器)的主要作用是把锁存比较电路的输出信号转化成逻辑电平(0 V或5 V)。如图2中第三部分所示,M8,M10,M11,M13,M14,M15组成差分自偏置电路,它能吸人和供出较大的电流,使比较器在驱动大的容性负载时速度不受摆率的限制。M9,M12组成一个反相器,用作附加的增益级,同时实现负载电容和自偏置差分放大器之间的隔离。要使输出缓冲级工作在线性区,输入信号的幅度一般要在1~3.5 V之间,所以在电路中串入M26管来提升锁存器输出电压的幅值。 2 电路仿真

在5 V电源的电压下,Vin-端加2.5 V参考信号,在Cadence软件平台下用Spec-tre工具对基于CSMC 0.5 μmCMOS工艺模型的电路进行仿真,得到比较器的增益、带宽、上升延时、下降延时、输入共模范围如图3所示。

|

用Cadence自带的Dracula工具对版图进行验证,通过设计规则检查(DRC),该版图符合CSMC0.5μmCMOS工艺的相关设计规则。通过电路图和版图的对照(LVS),版图中的器件及器件间的连接情况与电路图中相一致,保证了该版图是图2所示电路图的物理掩模图形集。此外,在做完DRC和 LVS后,版图的电气规则检查(ERC)也同时完成了,这是Dracula工具的一个

主要特点。ERC报告显示该版图中无短路、断路等电气规则错误。 4 结 语

在CSMC O.5μm CMOS工艺条件下,采用预放大器、锁存比较电路和输出缓冲级级联的锁存比较电路结构,设计了一个高速、高精度的高性能集成电压比较器,它具有低输入失调电压、低功耗的特点。完成从电路原理图设计到版图设计和验证(DRC,LVS)以及工艺角仿真和分析的整个设计流程。从仿真结果可以看出,这一高性能电压比较器适用于高速A/D转换器、高速数据传输器及高性能切换功率调节器等设备中。3 版图设计

集成电路的版图是芯片在实际制作时物理掩模图形的集合,是从电路原理图到实际芯片的关键过渡环节。版图的设计直接影响着芯片的最终性能。模拟集成电路版图的设计要求更高,它不仅有技术成分,还需要许多艺术性的布局和走线。

基于CSMC 0.5μm CMOS(N-Well硅栅)工艺设计的集成电压比较器版图如图4所示。其中电阻为制作在N-well中的P+扩散条;MOS管为NORMAL器件,其沟道宽长为多晶硅栅覆盖有源区部分的宽长。包围有源区的N+diff和P+diff,用来表明管子是NMOS管,还是PMOS管,版图面积为57μm×69 μm。 |

|