基于0.13μm CMOS工艺的快速稳定的高增益Telescop

近年来,软件无线电(Software Radio)的技术受到广泛的关注。理想的软件无线电台要求对天线接收的模拟信号经过放大后直接采样,但是由于通常射频频率(GHz频段)过高,技术上所限难以实现,而多采用中频采样的方法。而对于百兆赫兹的射频段,可以直接射频带通采样,这就要求采样系统有高的分辨率,而且其Nyquist频率要求比较高。本文设计的用于软件无线电台12 b A/D转换器中的高精度,高速运算放大器,采用了增益提高电路,在不影响频率响应的同时,得到普通运放所达不到的高增益。

1 高精度,高速度模数转换器对运算放大器指标的要求

为了达到12 b的A/D,第一级转换器出来的信号误差必须要小于后级所能辨认的最小精度,比如本文需要设计第一级的运算放大器,他后面一级的最小分辨力是10 b,那么,所设计的这个放大器的误差系数

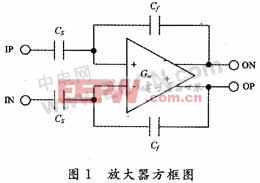

本文设计的运算放大器,用在12 b模数转换器中,模数转换器采用流水线结构,每一级的比特数为2.5 b,电路的方框图如图1所示。

图1中放大器接成负反馈形式,CS是输入采样电容,Cf是环路反馈电容,在2.5 b每级的应用中,CS=3Cf,闭环增益是4倍,这种2.5 b每级的结构,比传统的1.5 b每级的结构,放大器的数目减少了一半,可是由于闭环放大倍数变大了1倍,所以,反馈因子减小到一半,可以算出,运放的反馈因子大约为:

上式中的β为反馈系数,Copamp是运算放大器的反馈电容。

运算放大器可能会导致静态误差和动态误差,静态误差是由于运放的直流增益不可能为无穷大而导致的,而动态增益是由于运放的响应速度不可能为无穷快而导致的,经过分析,可以得到静态误差的方程,表示为直流增益ADC和反馈系数的函数,如下:

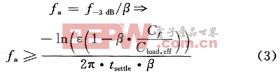

为了分析所设计的运算放大器的速度要求,需要把所能容忍的误差系数和电路的建立时间(Settling Time)联系起来,为了便于分析,我们先分析环路中只有一个主极点的情况,利用一阶响应三要素法,因为需要设计的模数转换器的工作频率是100 MHz,所以放大器的建立时间tsettle要小于4.5 ns,立即可以得到放大器的单位增益带宽为:

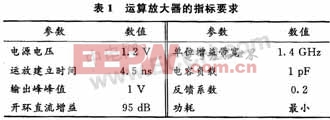

利用式(2),式(3),可以得到满足12 b A/D转换器要求的指标,如表1所示。

2 电压增益模型

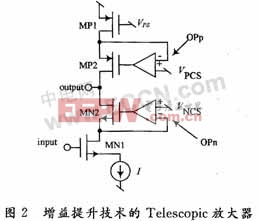

基本的增益提升技术应用于Telescopic放大器的电路如图2所示,图中的MN1,MN2,MP1和MP2组成了基本的Telescopic放大器,但是若不采取其他措施,在0.13 μm工艺的条件下,电压增益通常只能到60 dB,而从前面的分析来看,这样的增益是不够的。

图中的OPp和OPn是两个增益提高电路,有了这两个辅助的放大器之后,输出电阻可以表示成为:

式(4)中忽略了衬底效应和高阶效应,通过上面的方程,可以看出,电压增益在原来的基础上提高了很多。比如,0Pp和OPn的增益各为40 dB,那么加上原来主运放的增益,我们能够轻易得到100 dB的增益,完全满足12 b数模转换器的精度要求。

3 频率响应模型

增益提高技术,虽然大幅度提高了放大器的电压增益,但是电路变复杂了,频率响应必然受到影响,为了分析这种技术给主运放带来的影响,可以画出频率响应小信号等效电路图,如图3所示。

图3表明,电路的主极点是在输出点,负载电容大,输出电阻非常高,极点的位置在p1=1/(2πRoutCload)。主运放的第二个极点在点①处,电容是①点的寄生电容,Boot-ser的输入电容,M1管的Miller电容CGD,和M2管子的源极输入电容。位置为p2=gM2/(2πC1)。在频率响应中,一阶主极点引起的响应是指数逼近的响应,而其余的极点和零点则会引入非指数的响应,为了不过多地引入超调响应,或者是减慢响应速度,要求Booster除了要提高电压增益外,还不能影响运放的频率响应。文献[4,5]中给出了设计的要点,表现成不等式为:

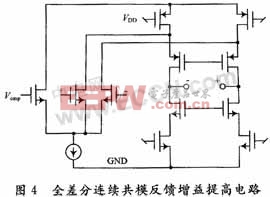

其中,ωu,main是主运放的单位增益带宽,ωb是增益提高运放的单位增益带宽,ωP2,main是主运放的次极点。式(5)表明,设计Booster时候,Booster不能太快,如果超过主运放的第二个极点,则会出现超调现象,同样也不能太慢,如果比主运放的3 dB带宽(第一个极点位置)还要慢,则会使整体的速度变慢。由于我们要设计的运放单位增益带宽为1.4 GHz,反馈系数为0.2,可以得到3 dB带宽约为300 MHz,故设计Bootser单位增益带宽为500 MHz,直流增益为40 dB。

电路图如图4所示。图中使用了连续时间的共模反馈电路。

4 电路的实现和讨论

使用上面提到的优化方法,本文在SMIC 0.13 μm工艺下设计了一个满足表1的运放。其版图设计如图5所示。对版图提取寄生电容并进行后仿真。其中开环时候间的小信号仿真图见图6,可以看到,直流增益为98 dB。闭环建立时间的仿真结果见图7,在

Telescopic 0 13 CMOS 工艺 相关文章:

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- C8051F320在USB设计中的应用(01-18)

- PCI9054芯片接口设计中若干问题的深入研究(01-18)

- 用CP2101将USB口扩展成串口(01-18)

- 单片机与串行AD转换器TLC0834的接口设计(01-22)