一种中速高精度模拟电压比较器的设计

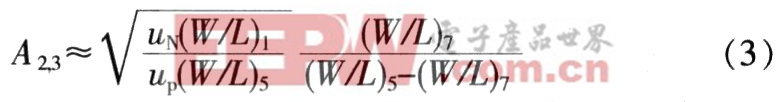

同样假设电路是完全对称的,则通过弱反馈补偿后,电路的增益约为:

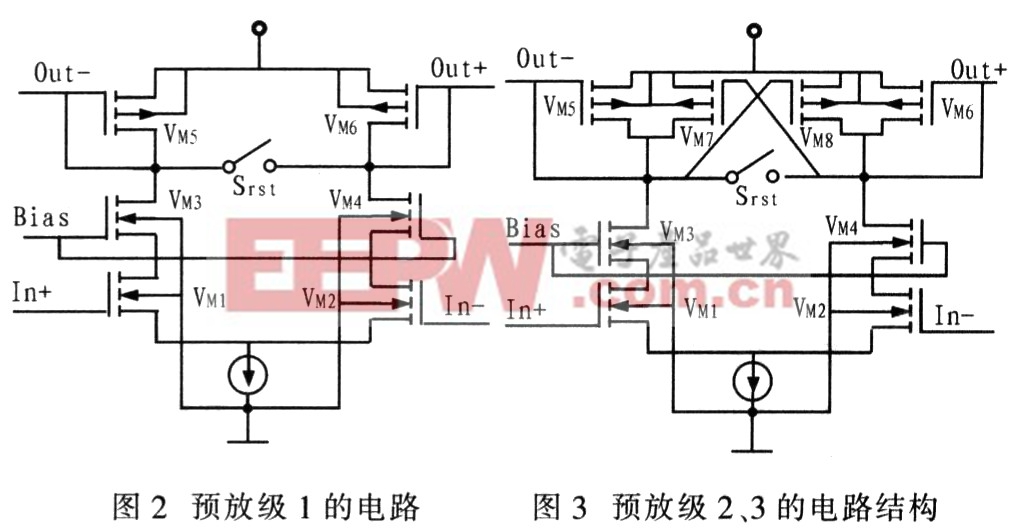

需要注意的是,迟滞比较器也是采用如图3所示的电路结构,所不同的是迟滞比较器使用了强正反馈机制。两者的区别就在于交叉的PMOS管VM7、VM8引入的电流相对于PMOS管VM5、VM6的电流的大小不同。当PMOS管VM7、VM8的电流大于PMOS管VM5、VM6的电流时,整个电路呈正反馈状态;反之,电路中的正反馈不足以抵消负反馈,整个电路呈负反馈状态。由于电路在大信号分析中PMOS管VM5~VM8的过载电压是相同的,因此它们的电流和宽长比成正比,故VM5的宽长比一定要大于VM7的宽长比才能实现弱正反馈。

2.4 锁存比较器与数字触发电路

锁存器实际上就是2个反相器首尾互连,由于利用反相器的正反馈的机制,输出信号与时间呈正指数关系变化,因此可将输入的小信号差量迅速放大到数字可识别的电平。同时,锁存器具有低功耗特点,因为它在一段时间内是不工作的,此时干路的开关被切断,因此无电流,功耗降低。然而,正是由于这样的工作特点。使锁存器工作时的输出状态并未持续一个时钟周期,为了串行数字输出正确以及给D/A转换器提供正确的置位信号,再生放大器后面应加适当的触发电路,以便在再生放大器工作期间正确输出持续时间为一个周期的比较结果。因此,设计出如图4所示的电路。

当φ为低电平时,输入信号In+和In-与锁存器接通,而锁存器与电源、地相连的开关均断开,锁存器处于感应输入信号阶段;同时,在数字触发电路中,高电平φ/使得开关管VMN7、VMN8导通接地,此时,低电平φ//分别通过VMP4、VMN4组成的反向器和VMP6、VMN6组成的反向器分别到达2个与非门的输入端并将其值置为高电平1,使得后级的数字RS触发器呈保持状态,持续保持输出不变。

当φ为高电平时,输入信号In+和In-与锁存器断开,而锁存器与电源、地相连的开关接通,锁存器处于正反馈工作段,输出信号Out+、Out-与时间呈正指数关系变化,使输出迅速达到电源电压或低电平,直接满足数字输出要求;同时,在数字触发电路中,低电平φ/使得开关管VMN7、VMN8关断,高电平 φ//别使VMP4、VMP6关断和VMN4、VMN6导通,因此,此时2个与非门的输入端便分别成为了由VMP3、VMN3组成的反向器和VMP5、 VMN5组成的反向器的输出端,其取值直接由反向器的输入Out+、Out-决定.使得后级的数字RS触发器根据输入的变化而变化,得到正确输出。

3 比较器的工作时序与仿真

考虑到要最大限度降低锁存器和数字触发电路部分对前面的模拟电路部分产生的干扰,以及使比较器在每个比较周期完成后迅速复位,必须使用复位控制。该比较器工作过程依次分为失调校准和比较两个阶段。比较阶段由数个比较周期组成,在每个比较周期开始时(除了失调校准结束后的第一个比较周期),预放级1~3和锁存器在复位信号rst的作用下进行复位操作;在每个比较周期结束时,锁存器在锁存信号西作用下锁存放大信号。

仿真中使用Hspice进行瞬态仿真验证,为了降低比较器功耗和干扰,设定锁存信号φ的有效信号占空比为1:8,要达到20 MHz的速度,则锁存信号的周期应为50 ns。为此。设定Vcm=1.2 V,而Vin每50 ns变化一次,从0 ns到250 ns分别为1.2 V,1.200 2 V,1.199 8 V,2 V,1.199 8 V,其中,0~50 ns期间,比较器处于失调校准阶段,之后每个比较周期为50 ns。

当预放级1~3无输入失调,存在20 mV输入失调时,比较器的仿真结果分别如图5和图6所示,其中西为锁存信号,rst为复位信号,Out为比较器输出,Vo3+、Vo3-为预放级3的输出信号。由仿真结果知,比较器在上述的Vcm和Vin的输入下,能够在20 MHz的输人信号频率下准确输出结果。因此,该比较器既能够准确的识别0.2 mV的小信号,也能在0.8 V的大信号输入下具有很强恢复能力。而当预放级1~3都有20 mV输入失调时,从图5看出,预放级3的输出会在复位信号后产生波动,但由于使用了恰当的失调校准技术,波动后的信号依然能够快速复位,比较器依然能够准确有效地辨别电压。也就是说,20 mV输入失调并没有淹没小至0.2 mV的小信号输入差值,失调校准技术取得预期效果。

4 结束语

在传统的多级结构的基础上,实现中速高精度模拟电压比较器。通过仿真,比较器达到各项预定指标,在20 mV输入失调下精度达到0.2 mV,速度20 MHz,功耗约1 mW。

- 一种新型高精度CMOS带隙基准源的设计(09-12)

- 高精度自动校时钟在中波转播台中的应用(10-25)

- 基于DPWM的高速高精度积分型模数转换器(11-05)

- 高速高精度流水线模数转换器的设计(12-09)

- 高精度的温度传感电路设计(03-09)

- 基于TMS320F2808的高精度UPS电源锁相技术(11-16)